声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

寄存器

+关注

关注

30文章

5025浏览量

117705 -

时钟

+关注

关注

10文章

1479浏览量

130304 -

时序

+关注

关注

5文章

356浏览量

36955

发布评论请先 登录

相关推荐

Modelsim SE 进行时序仿真及altera库的添加 [转]

Modelsim进行时序仿真。 第一部分介绍Quartus II自动调用Modelsim进行时序仿真的操作过程;第二部分介绍altera仿真库(Verilog)的添加操作过程;第三部分简单的介绍一下

发表于 02-01 11:37

通向FPGA之路---七天玩转Altera教程

本系列教程的宗旨是在力求全面介绍Altera及其QuartusII软件原理的基础上,对何如使用Altera FPGA进行基础设计、时序分析、验证、优化四大方面进行

发表于 12-04 14:36

ALTERA FPGA/CPLD高配学习指南:入门和高级篇,教程十讲全集

/cpld的设计和优化技巧。在讨论fpga/cpld设计指导原则的基础上,介绍了altera器件的高级应用;引领读者学习逻辑锁定设计工具,详细讨论了时序约束与静态时序分析方法;结合实例

发表于 05-14 14:50

Altera FPGA教程之让你七天学会Altera FPGA的时序分析

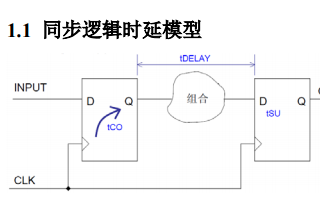

网上关于 Altera 的教程很多,可谓浩如烟海。大体来说有两类:一是,step by step 的指导如何操作 Quartus 软件,这类方法的优点是上手快,但却有知其然不知其所以然之惑;二是,从一个很高的起点分析一些具体问题,优点是有深度,但也把大部分初学者拒之门外,

发表于 09-13 08:00

•51次下载

altera时序约束与分析

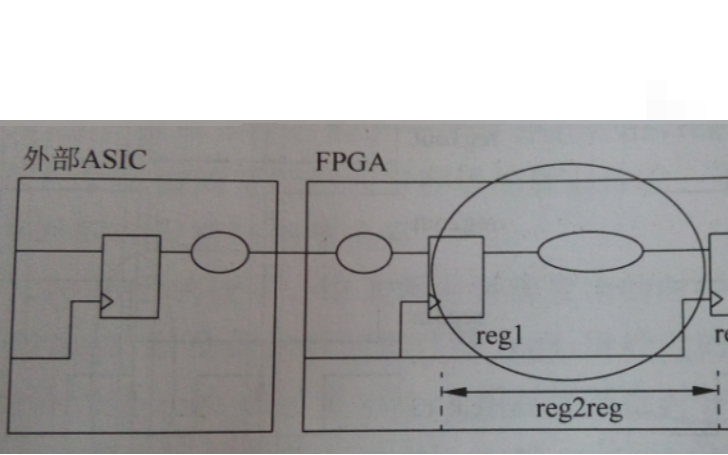

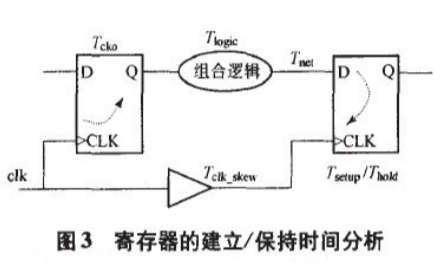

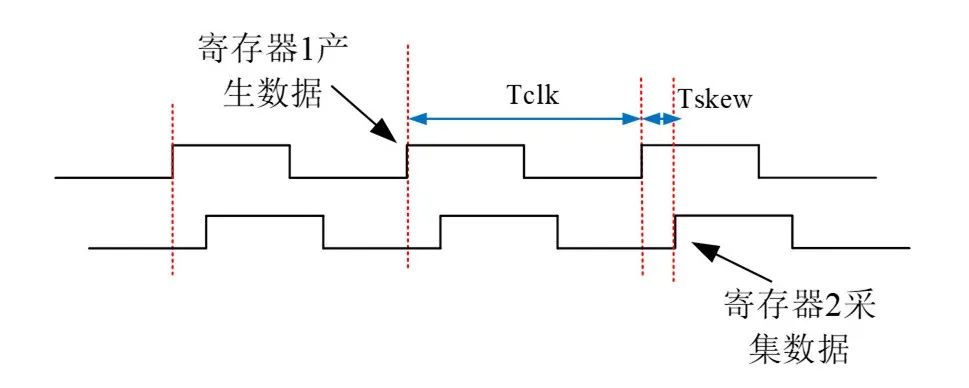

时序分析的主要对象是:在REG2中,时钟信号CLK经过路径③的有效沿,与从REG1寄存器输出的数据经过路径①到达REG2的D端时的关系。

ALTERA系列的FPGA时序分析

其中前三类路径是和内部寄存器reg和时钟CLK有关的,因此还需关注内部数据信号与时钟锁存沿的建立时间和保存时间(具体见时序分析一),而最后一类信号的传输通常不经过时钟,因此它的约束也相对简单

发表于 01-08 16:47

•13次下载

FPGA的静态时序分析详细讲解分析

任何学FPGA的人都跑不掉的一个问题就是进行静态时序分析。静态时序分析的公式,老实说很晦涩,而且总能看到不同的版本,内容又不那么一致,为了彻底解决这个问题,我研究了一天,终于找到了一种

发表于 01-12 17:48

•19次下载

altera时序分析基础项目讲解

altera时序分析基础项目讲解

评论