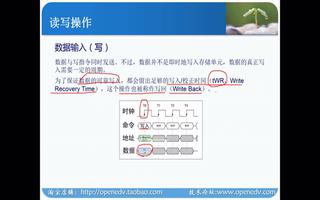

所谓的影响性能是并不是指SDRAM的带宽,频率与位宽固定后,带宽也就不可更改了。但这是理想的情况,在内存的工作周期内,不可能总处于数据传输的状态,因为要有命令、寻址等必要的过程。但这些操作占用的时间越短,内存工作的效率越高,性能也就越好。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21307浏览量

593113 -

SDRAM

+关注

关注

7文章

409浏览量

54728 -

时序

+关注

关注

5文章

356浏览量

36955

发布评论请先 登录

相关推荐

SDRAM理论篇之基础知识及操作时序讲解

了,如果在这篇文章中出现了某些错误,还希望您及时批评指出。另外,Kevin也会在接下来的一篇博文中分享怎么来写SDRAM的控制器,也就是怎么来把这篇文章中的这些操作用代码写出来。参考书籍:1.《高手进阶 终极内存技术指南》2.

发表于 01-16 18:06

SDRAM的基础知识和操作时序

是怎么来把这篇文章中的这些操作用代码写出来。参考书籍:1.《高手进阶 终极内存技术指南》2. 厂商官方手册转载请注明:邓堪文博客 » SDRAM理论篇之基础知识及

发表于 01-24 06:35

SDRAM的原理和时序

SDRAM的原理和时序

SDRAM内存模组与基本结构 我们平时看到的SDRAM都是以模组形式出现,为什么要做成这种形式呢?这首先要接触到两个概念:物理Bank与芯片位宽

发表于 03-11 14:43

•167次下载

一种基于FPGA的SDRAM设计与逻辑时序分析

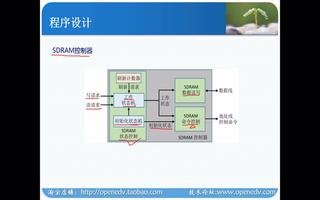

控制器,在介绍控制器的逻辑结构的基础上,对FPGA与SDRAM间数据通信进行了时序分析,实现SDRAM 带有自动预充电突发读写和非自动预充电整页读写。

发表于 11-18 12:42

•2071次阅读

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文

,SDRAM的原理和时序,SDRAM控制器,动态随即存储器SDRAM模块功能简介,基于FPGA的SDRA

发表于 12-25 08:00

•56次下载

正点原子开拓者FPGA:SDRAM时序操作(2)

通常DRAM是有一个异步接口的,这样它可以随时响应控制输入的变化。而SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。

正点原子FPGA之SDRAM:SDRAM操作时序(2)

正点原子FPGA之SDRAM:SDRAM操作时序(2)

评论