声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21301浏览量

593101 -

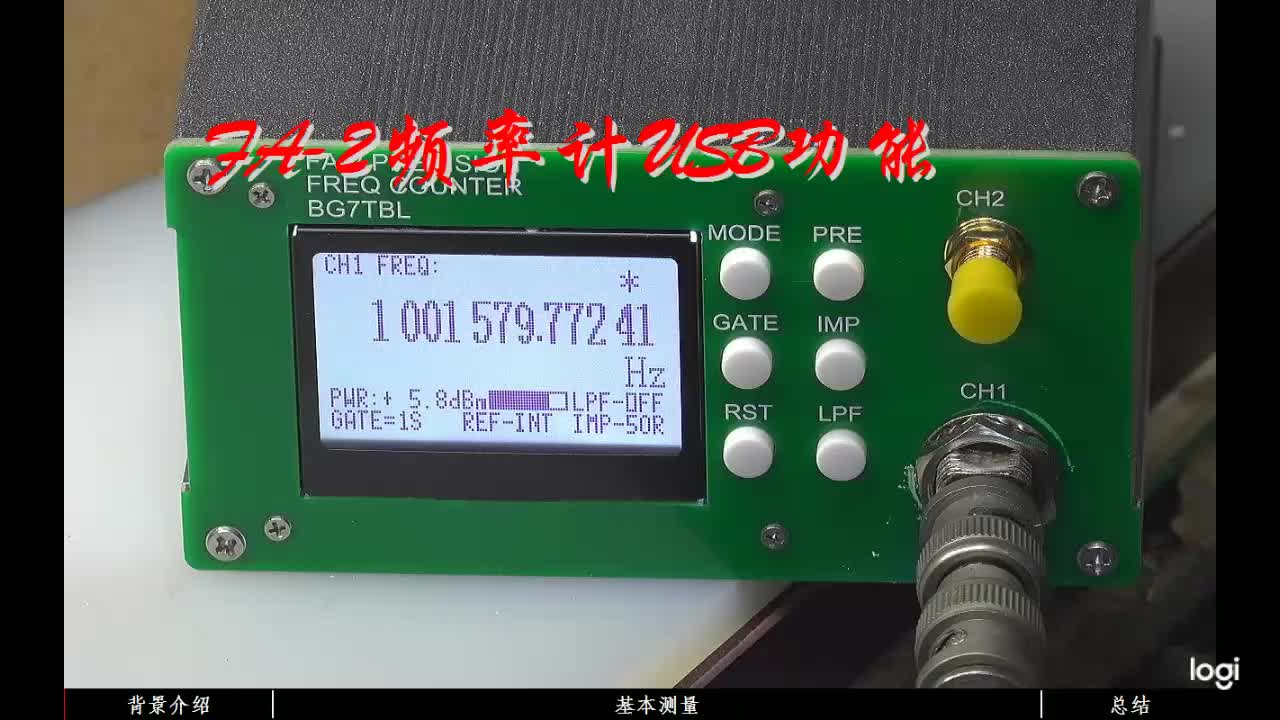

频率计

+关注

关注

8文章

166浏览量

43888 -

计数器

+关注

关注

32文章

2121浏览量

92941

发布评论请先 登录

相关推荐

基于FPGA设计频率计方案介绍分享

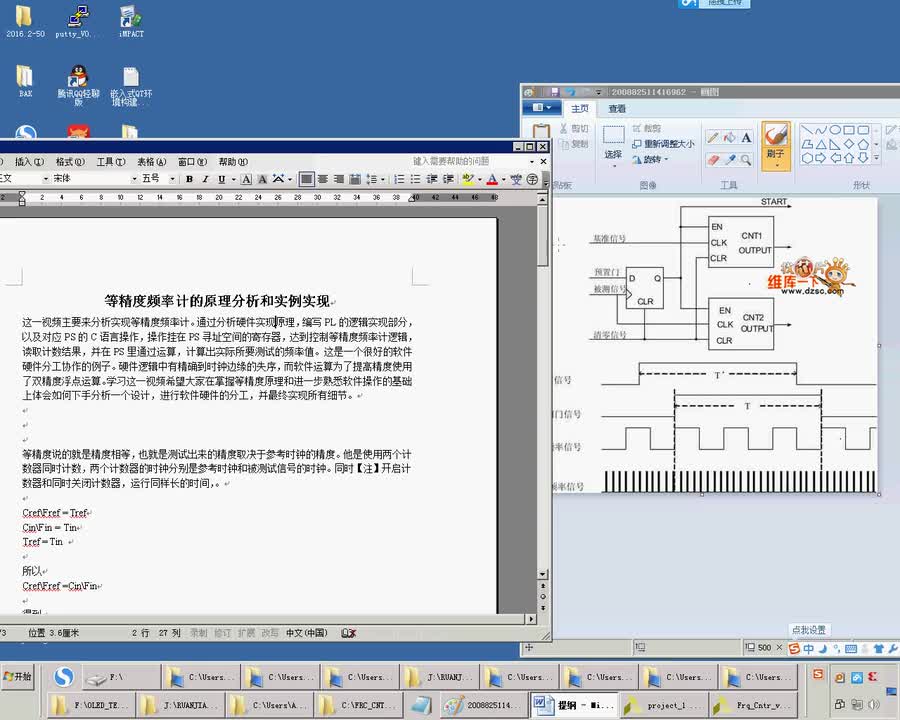

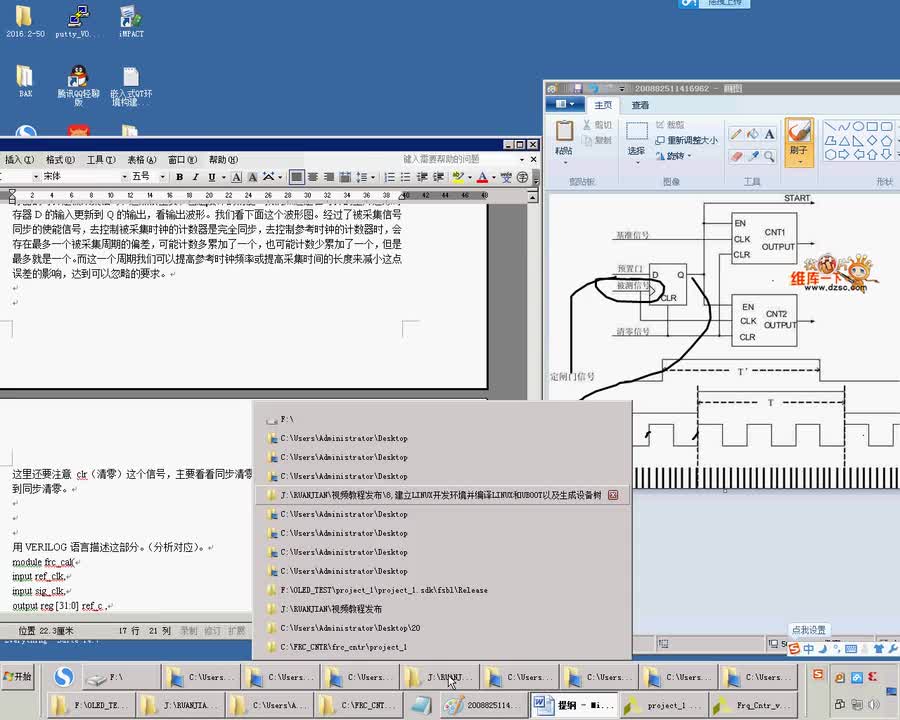

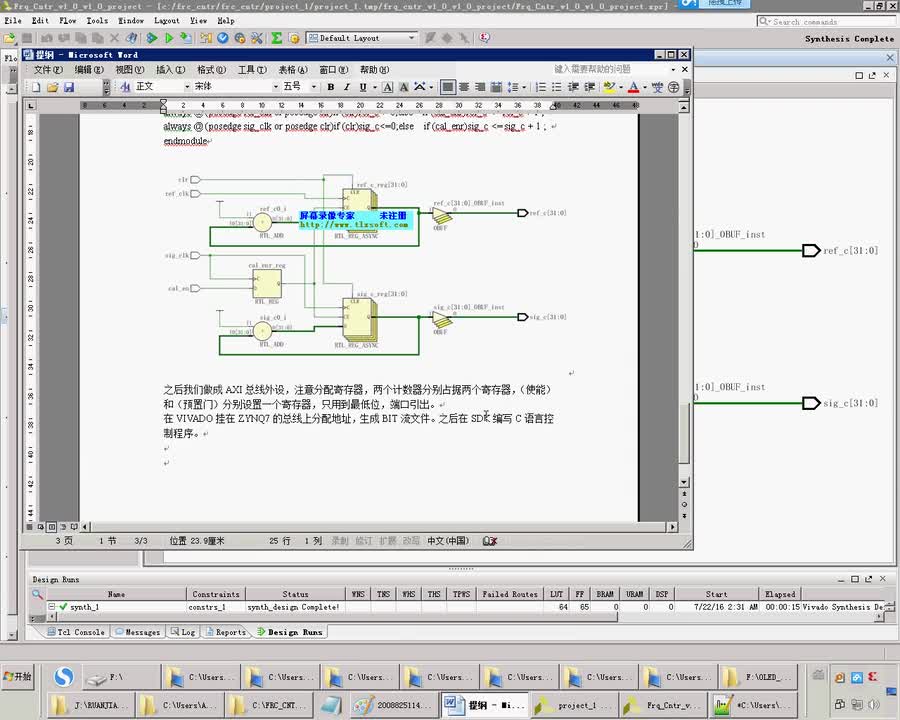

数字电路识别的脉冲信号,然后通过计数器计算这一段时间间隔内的脉冲个数,将其换算后显示出来,这就是数字频率计的基本原理。

系统设计图如下所示:

发表于 03-31 16:22

频率计精度问题

我用51单片机的内部定时/计数器做频率计实验,但是在仿真时出现较大的误差,如从int0引入外部脉冲,如设置频率为500Hz实际测量为542Hz,设置为1k,实际测量为1084hz。具体的软件算法

发表于 05-01 16:24

【正点原子FPGA连载】第二十二章频率计实验-领航者ZYNQ之FPGA开发指南

原子公众号,获取最新资料第二十二章频率计实验数字频率计是一种基本的测量仪器,被广泛应用于航天、电子、测控等领域。基于传统测频原理的

发表于 09-27 17:54

【正点原子FPGA连载】第二十二章频率计实验-领航者ZYNQ之FPGA开发指南

原子公众号,获取最新资料第二十二章频率计实验数字频率计是一种基本的测量仪器,被广泛应用于航天、电子、测控等领域。基于传统测频原理的

发表于 09-28 18:10

基于FPGA+stm32的的等精度频率计的设计资料分享

导致测量的时间过长。2.占空比测量:这里借鉴了基于FPGA的简易频率计设计这篇文章的测量方法。通过门控时间内,对PLL倍频的200MHz时钟clk_200计数,读出待测信号连续的四个边沿的计数值,通过

发表于 02-09 07:07

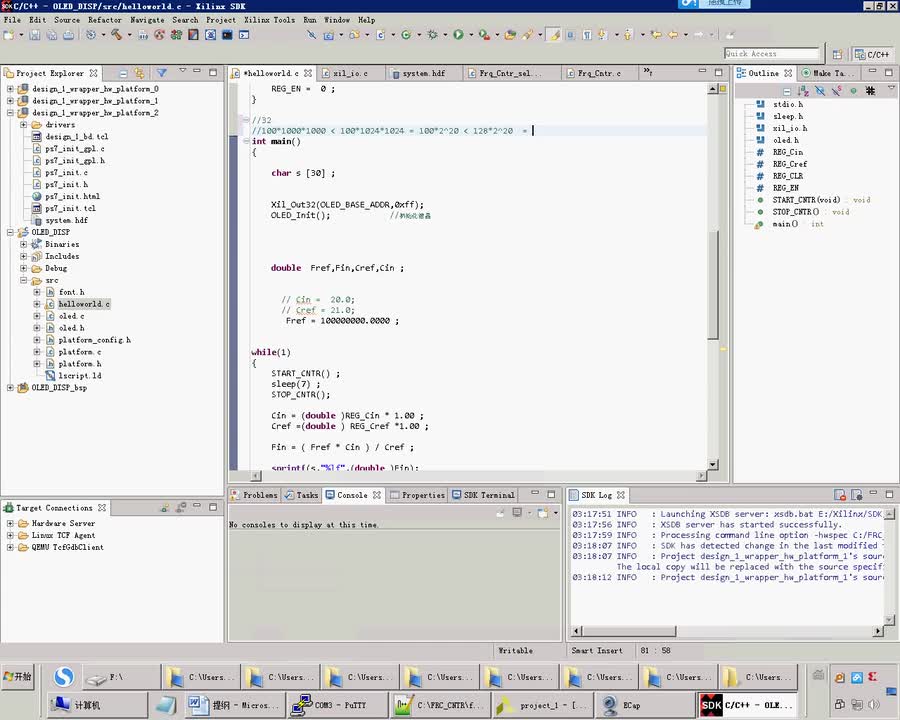

正点原子FPGA之等精度频率计实验:频率计计算

正点原子FPGA之等精度频率计实验:频率计计算

评论