声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

处理器

+关注

关注

68文章

18242浏览量

222030 -

FPGA

+关注

关注

1602文章

21299浏览量

593091 -

逻辑

+关注

关注

2文章

818浏览量

29292

发布评论请先 登录

相关推荐

浮点处理器相对于定点处理器有何不同

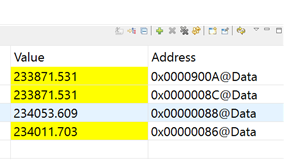

对程序做出改动。浮点处理器相对于定点处理器有如下好处: 编程更简单 性能更优,比如除法,开方,FFT和IIR滤波等算法运算效率更高。 程序鲁棒性更强。 一、IEEE754格式的浮点数

FPGA实现高速FFT处理器的设计

FPGA实现高速FFT处理器的设计介绍了采用Xilinx公司的Virtex - II系列FPGA设计高速FFT处理器的实现方法及技巧。充分利用Virtex - II芯片的硬件资源,减少

发表于 08-12 11:49

【FPGA干货分享六】基于FPGA协处理器的算法加速的实现

。没有通用的协处理器库,即使是存在这样的库,将依然难以简单地将协处理器与一个CPU(例如Pentium 4)连接。Xilinx Virtex-4 FX FPGA拥有一个或两个Power

发表于 02-02 14:18

FPGA实战演练逻辑篇7:FPGA的优势

瞬间便可搞定。因此,尤其对于一些大吞吐量、重复执行的数据传输、处理操作,软件往往无法胜任,非要借助微处理器所支持的专用的硬件加速模块或者FPGA

发表于 03-26 11:00

基于FPGA控制的多DSP并行处理系统

FPGA具体的处理流程嵌套在DSP的信号处理流程中。4片DSP主要完成信号的处理,大致的系统设计流程如图3所示。4片DSP并行工作时,总线仲

发表于 05-21 05:00

基于FPGA分布式算法的低通FIR滤波器该怎么设计?

传统数字滤波器硬件的实现主要采用专用集成电路(ASIC)和数字信号处理器(DSP)来实现。FPGA内部的功能块中采用了SRAM的查找表(lo-ok up table,LUT)结构,这种

发表于 08-29 06:43

基于并行分布式算法的滤波器怎么实现?

传统数字滤波器硬件的实现主要采用专用集成电路(ASIC)和数字信号处理器(DSP)来实现。FPGA内部的功能块中采用了SRAM的查找表(lo-ok up table,LUT)结构,这种

发表于 10-22 07:14

什么是DSP,DSP处理器有什么特点?

乘法器、乘加器、乘累加器,并运用在绝大多数DSP算法上。显然,这里的DSP块,只是一个可配置的乘加单元,并非前面所说的DSP处理器。其实FPGA

发表于 09-04 10:31

SimpleWiFi相对于常见的UARTWiFi具有哪些优势?

工业领域的特点有哪些?WiFi为什么会被用于工业控制中?SimpleWiFi相对于常见的UARTWiFi具有哪些优势?

发表于 07-19 08:17

3GPP R4相对于R99的优势

3GPP R4相对于R99的优势

相对于传统电路交换网络,软交换网络可以实现更简单的目标网络结构,主要是从节约运营成本、易于维护和保

发表于 06-13 22:27

•1061次阅读

微处理器系统中连接简单的被动串行配置方法和被动并行异步配置方法

成本。微处理器根据不同的程序应用,采用不同的配置数据对FPGA进行配置,使FPGA实现与该应用有关的特定功能。详细介绍了微处理器系统中连接简单

发表于 11-06 11:10

•1次下载

FPGA相对于CPU和GPU而言有着比较明显的优势

FPGA相对于CPU和GPU,在进行感知处理等简单重复的任务的时候的优势很明显,按照现在的趋势发展下去,FPGA或许会在未来取代机器人开发中

发表于 12-20 14:39

•2439次阅读

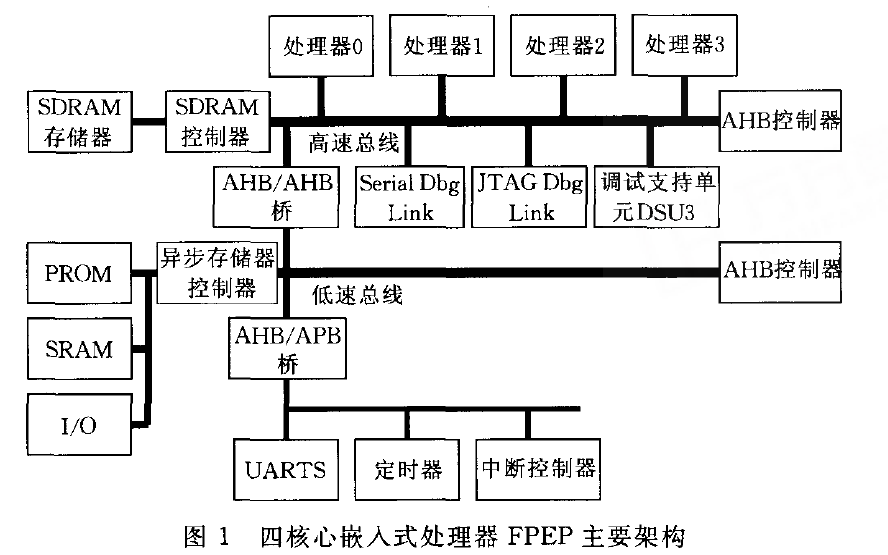

如何使用FPGA实现嵌入式多核处理器及SUSAN算法并行化

出了四核心嵌入式并行处理器FPEP的结构设计并建立了FPGA验证平台.为了对多核处理器平台性能进行评测,提出了基于OpenMP的3种可行的图像处理

发表于 02-03 16:26

•8次下载

FPGA简单入门和逻辑块与相对于处理器的并行操作

FPGA简单入门和逻辑块与相对于处理器的并行操作

评论