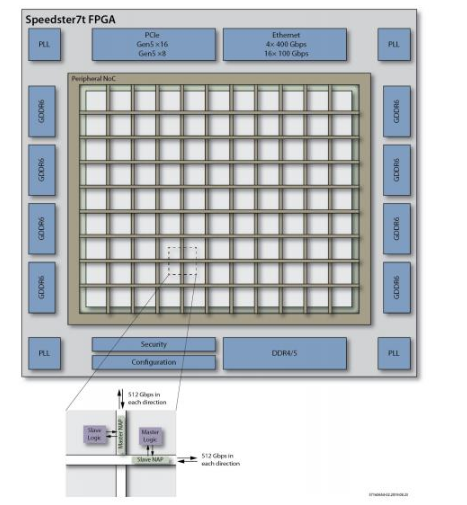

在遵循管脚特定的规则和约束的同时,可以在 PCB 上的多个 FPGA 之间自动优化信号管脚分配。减少布线层数,最大限度地减少 PCB 上的交叉数量并缩短总体走线长度,以及减少信号完整性问题,从而提高完成率并缩短 FPGA 的布线时间。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21308浏览量

593119 -

pcb

+关注

关注

4220文章

22468浏览量

385661

发布评论请先 登录

相关推荐

FPGA布局布线的可行性 FPGA布局布线失败怎么办

随着电子技术的进步.FPGA逻辑电路能完成的功能越来越多,同样也带来了一个很大的问题,即逻辑电路的规模越来越大,这意味着RTL代码到FPGA的映射、布局布线所花费的时间也越来越长。

Arm 宣布推出全新汽车技术,可缩短多达两年的人工智能汽车开发周期

的开发时间、降低成本,并带来最大的灵活性 Arm 生态系统首次实现在物理芯片就绪前就可基于虚拟原型解决方案启动软件开发,由此可缩短多达两年的开发周期 Arm 控股有限公司(纳斯达克股票代码:ARM,以下简称“Arm”)今日携手生态系统合作伙伴推出最新的 Arm 汽车增

发表于 03-14 13:34

•85次阅读

Arm宣布推出全新汽车技术,可缩短多达两年的人工智能汽车开发周期

Arm 携手生态伙伴推出了最新的 Arm 汽车增强 (AE) 处理器和虚拟平台,让汽车行业在开发伊始便可应用,助力缩短多达两年的开发周期。

fpga布局布线算法加速

现代电子设备中,针对复杂的数字电路,FPGA(Field-Programmable Gate Array)是一种非常优秀的可编程逻辑器件。在FPGA的设计过程中,布局布线算法是关键步骤之一,其主要

电机启动时间一般是多久?怎么缩短启动时间呢?

电机启动时间一般是多久?我这个电机是132KW的,还有就是怎么缩短启动时间,1S内能启动吗?请高手解答

说了那么多,我还是没明白启动时间是多长,斑竹一般电机多长

发表于 11-16 08:19

关于PCB布局和布线的设计技巧

随着PCB 尺寸要求越来越小,器件密度要求越来越高,PCB 设计的难度也越来越大。如何实现PCB 高的布通率以及缩短设计时间,在这笔者谈谈对PCB 规划、布局和布线的设计技巧。

发表于 11-09 15:24

•185次阅读

FPGA在一个时钟周期可以读取多个RAM数据吗?

FPGA在一个时钟周期可以读取多个RAM数据吗?如何理解FPGA中存放程序的RAM? FPGA在一个时钟周期可以读取多个RAM数据

FPGA时序约束之建立时间和保持时间

FPGA中时序约束是设计的关键点之一,准确的时钟约束有利于代码功能的完整呈现。进行时序约束,让软件布局布线后的电路能够满足使用的要求。

发表于 08-14 17:49

•823次阅读

电容器负载电阻降低放电时间缩短的原因

当电容器受到负载电阻的影响时,它的放电时间会缩短。本文将详细探讨电容器负载电阻降低放电时间缩短的原因,并分析其中的关键因素。

如何缩短多个FPGA的布线时间

如何缩短多个FPGA的布线时间

评论