通过确定 DDR 1/2/3 和 LPDDR1/2/3 设计中常有的时序和 SI 等问题来减少设计和调试周期。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

存储器

+关注

关注

38文章

7144浏览量

161976 -

DDR

+关注

关注

9文章

677浏览量

64232 -

设计

+关注

关注

4文章

814浏览量

69701

发布评论请先 登录

相关推荐

完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表

电子发烧友网站提供《完整DDR,DDR2,DDR3 和LPDDR3 存储器电源解决方案同步降压控制器数据表.pdf》资料免费下载

发表于 04-09 09:49

•0次下载

STM32F103DMA模块存储器到存储器可以实现循环吗?

STM32F103 参考手册中循环模式部分描述:DMA模块存储器到存储器不能与循环模式同时使用。但是经过实际测试,是可以实现循环的,请问怎么理解这句话呢?

发表于 04-02 06:23

具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方案数据表

电子发烧友网站提供《具有同步降压控制器、2A LDO和缓冲基准的TPS51916完整DDR2、DDR3、DDR3L和DDR4存储器电源解决方

发表于 03-13 11:24

•0次下载

TPS65295完整 DDR4 存储器电源解决方案数据表

电子发烧友网站提供《TPS65295完整 DDR4 存储器电源解决方案数据表.pdf》资料免费下载

发表于 03-06 10:17

•0次下载

如何使用SCR XRAM作为程序存储器和数据存储器?

1) 允许一个物理内存(即 XRAM) 可同时作为程序存储器和数据存储器进行访问

如何使用 SCR XRAM 作为程序存储器和数据存储器。

1) 用于

发表于 01-30 08:18

基于PDN共振峰的最坏情况数据模式分析电源完整性对FPGA DDR4存储器接口中的信号完整性的影响

电子发烧友网站提供《基于PDN共振峰的最坏情况数据模式分析电源完整性对FPGA DDR4存储器接口中的信号完整性的影响.pdf》资料免费下载

发表于 09-13 09:56

•0次下载

AXI内部存储器接口的功能

库的慢-慢工艺点对块进行合成,以200 MHz的目标速度确认时序特性。

接口存储器端口上的信号符合RAM编译器为TSMC CL013G工艺技术生产的单端口同步存储器组件所要求的时序要求

发表于 08-21 06:55

不同的存储器技术介绍 如何选择正确的存储器技术

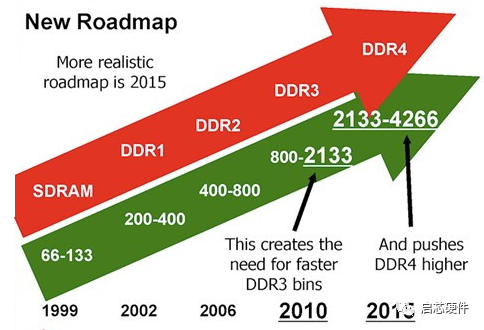

技术,每种技术都具有不同的特性和高级功能。双数据速率 (DDR) 同步动态随机存取存储器 (SDRAM) 已成为主系统存储器最主流的存储器技术,因为它使用电容器作为

发表于 08-17 09:54

•477次阅读

PLC的存储器、I/O单元、I/O扩展接口、外设接口和电源简介

可编程控制器的存储器由只读存储器ROM、随机存储器RAM和可电擦写的存储器EEPROM三大部分构成,主要用于存放系统程序、用户程序及工作数据。

单板硬件设计:存储器( NAND FLASH)

。

EEPROM的全称是“电可擦除可编程只读存储器”,即Electrically Erasable Programmable Read-Only Memory。是相对于紫外擦除的rom来讲的。但是今天已经存在多种

发表于 05-19 15:59

如何解决DDR存储器接口存在的问题

如何解决DDR存储器接口存在的问题

评论