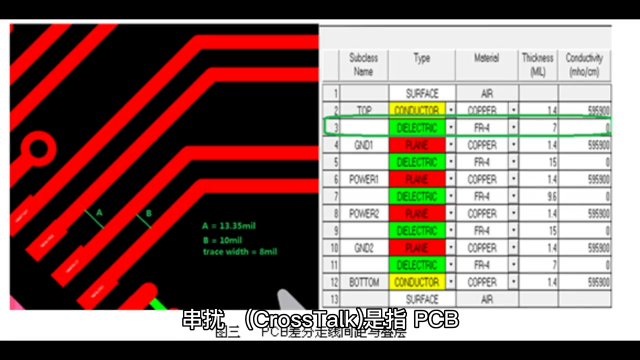

使用 HyperLynx® 可以轻松地查找并修复 PCB 串扰问题。从 PCB Layout 导出设计后,以批量模式和/或交互模式运行仿真,从而确定潜在的串扰问题。利用 BoardSim 的耦合区检视器,您可以准确地找到耦合度最高的网络区域所在的位置。此外,将网络导出到 LineSim,以编辑耦合部分并消除串扰问题。然后,确定需要对 Layout 做出的更改。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

pcb

+关注

关注

4216文章

22446浏览量

385271 -

网络

+关注

关注

14文章

7248浏览量

87409

发布评论请先 登录

相关推荐

【新手指南】自己焊接pcb电路板需要哪些工具

PCB电路板焊接工具是指用于在印刷电路板(PCB)上进行焊接操作的工具。捷多邦小编刚好整理了一些自己焊接pcb电路板所需要的

要画好PCB,先学好信号完整性!

倾向于更低的核心电压和更高的工作频率,这就导致了急剧上升的边缘速率。无端接设计中的边缘速率将会引发反射和信号质量问题。

串扰

在高速信号设计中,密集路径往往会导致串扰——在

发表于 02-19 08:57

EMC之PCB设计技巧

技巧

技巧1:将PCB接地

降低EMI的一个重要途径是设计PCB接地层。第一步是使PCB电路板总面积内的接地面积尽可能大,这样可以减少发射、串扰

发表于 12-19 09:53

ADC电路中造成串扰的原因?如何消除串扰?

是ADI的SAR型 18位单通道全差分输入的ADC。ADC的后端是MCU,MCU将数字信号处理之后再画到显示屏上显示实时波形。

调试发现显示的信号有串扰,表现为某一路信号悬空之后,相邻的那一路信号

发表于 12-18 08:27

AD9229-65在上电使用时发现AD的输入端有很多信号串扰的原因?

AD9229-65的使用问题:AD时钟给的是50MHz,在上电使用时发现AD的输入端有很多信号串扰在上面,采样后数据就出错了,如果设置AD工作在pown模式(掉电模式)下,AD输入端的信号就非常干净没有干扰,AD前端差分电路如下图

发表于 12-14 07:56

利用示波器观察AD7738芯片的RDY和DOUT管脚,为什么两管脚信号互相串扰?

利用示波器观察AD7738芯片的RDY和DOUT管脚,为什么两管脚信号互相串扰?RDY信号和DOUT在RDY管脚都能看到两个信号,在DOUT管脚也都能看到两个信号。是不是芯片坏了?

发表于 12-13 07:34

在使用AD9251-40做FPGA控制采集时发现由ADC采集上来的信号有非常大的串扰是为什么?

在使用AD9251-40 做FPGA 控制采集时候发现由ADC采集上来的信号有非常大的串扰,怀疑是ADC差分时钟的问题。所用FPGA 型号是EP4CE40F23I7, 采用方式是直接用FPGA IO 口产生LVDS差分时钟输出给ADC,请问一下各位高手这里是否会出问题

发表于 12-05 07:33

ADI PCB设计秘籍的PDF电子书分享

本《PCB设计秘籍》工具书共包含17个章节,以ADl(亚德诺半导体)公司官方网站、AD中文技术论坛、的PCB设计内容资料为基础资料来源,按PCB布局布线、散热技巧、接地指导、抗

发表于 09-21 07:55

PCB烘烤温度与时间的确定方法

PCB在制造完成之后都有一个保质期,超过这个保质期就需要对PCB进行烘烤,要不然容易使PCB在SMT上线生产时,产生PCB爆板的问题。 一、PCB

DDR跑不到速率后续来了,相邻层串扰深度分析!

拉到6mil以上不更好了。呃,这个……只能回答你们,PCB设计是需要多种因素来权衡,拉到6mil的串扰肯定会更好,但是信号离地平面近了,线宽需要减小才能控到之前的阻抗,近到2mil压根就控不到阻抗

发表于 06-06 17:24

使用HyperLynx工具确定和解决PCB串扰问题

使用HyperLynx工具确定和解决PCB串扰问题

评论