下一代ASIL B(D)自主驾驶系统将使用符合ISO 26262标准的缓存一致性互连IP和非一致性互连IP来实现。

美国加利福尼亚州坎贝尔2019年4月26日消息—Arteris IP是经过实际验证的创新性片上网络(NoC)互连知识产权(IP)产品的全球领先供应商,宣布,MobileEye已购买Arteris IP 的NCore缓存一致性互连产品、flexNOC互连产品以及NCore和flexNOC Resilience软件包等多项产品,用于功能安全和人工智能(AI)硬件加速。Arteris IP的这些互连技术产品将成为MobileEye的新一代EyeQ系统级芯片(SoC)——符合下一代ISO 26262 ASIL B(D)级别安全标准的器件——片上通信的主要部件。

MobileEye团队是与Arteris IP合作最久、最有创新性的客户之一,它在2010年首次购买Arteris的FlexNoc互连IP产品,并且把该产品陆续用于Eyeq3、Eyeq4和Eyeq5等系列系统级芯片( SoC),作为片上互连。

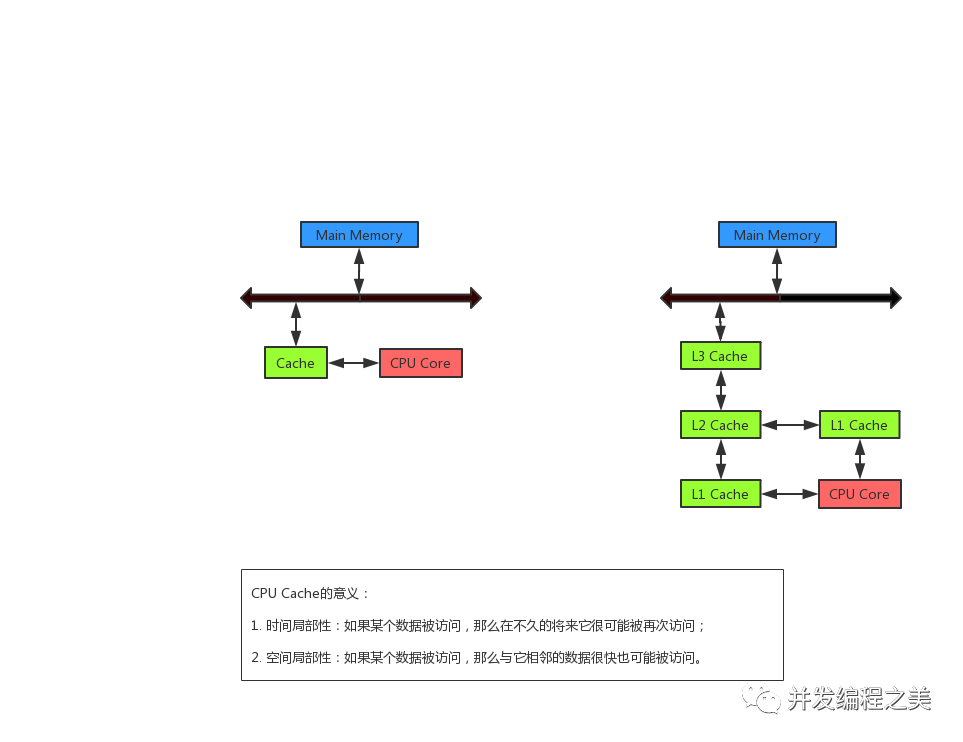

Mobileye之所以选择NCore缓存一致性互连和配套的Resilience软件包,是因为它们能够实现多个片上缓存一致性子系统,包括专有的异构可编程硬件加速器。这些子系统协同工作,以加快执行速度,增大计算带宽,并降低机器学习和人工智能算法的功耗,这些算法在汽车行驶时几乎是无延迟地实时执行。

NCore之所以能够做到这些,是因为它有独特的高度可配置的NCore代理缓存,可以将多个硬件加速器组织成集群,在缓存一致性系统中它们是完全一致对等的。MobileEye在用自己的二级客制式高速缓存设计这些处理单元集群时,高度可配置的NcoreC高速缓存一致性互连能够节省时间和精力,并且把通信集中到一个缓存目录中,从而优化系统带宽的使用。

Mobileye工程副总裁Elchanan Rushinek说:“我们之所以选择Arteris的缓存一致性互连,是因为它具有独特的代理缓存,并且能够支持我们的独一无二的人工智能加速器的高性能、低功耗、缓存一致集群。”他表示,“根据我们以往使用FlexNoc和FlexNoc功能安全Resilience软件包的经验,我们相信,Arteris IP符合ISO 26262标准,是性能最好、最安全的片上网络IP (NoC IP)。”

Arteris IP总裁兼行政总监K.Charles Janac说:“在城市里用于驾驶的ADAS系统级芯片的复杂程度令人难予置信,以致几年后,汽车将成为装了轮子的超级计算机。这种芯片需要最先进、最灵活、适应性最强的互连来执行多个同时运作的神经网络和机器学习算法,同时确保数据得到保护,并符合ISO 26262标准对功能安全的要求。”他表示,“我们已经与MobileEye合作设计了几代系统级芯片(SoC),我们拥有包括NCore、Flexnoc、Piano和Resilience产品在内的一系列互联IP产品,成为MobileEye最新的系统级芯片项目的战略伙伴,对我们感到十分荣幸。”

-

芯片

+关注

关注

446文章

47728浏览量

409019 -

Mobileye

+关注

关注

2文章

122浏览量

33657 -

自主驾驶

+关注

关注

0文章

17浏览量

4593

发布评论请先 登录

相关推荐

深入理解数据备份的关键原则:应用一致性与崩溃一致性的区别

DDR一致性测试的操作步骤

求助,为什么miniWiggler的JTAG信号映射与设备端(TC397)不一致?

Redis缓存与Mysql如何保证一致性?

AD9826存偏置电压不为0,并且一致性较差的原因?

256核!赛昉发布全新RISC-V众核子系统IP平台

ADA4960工作在单端输入-差分输出模式下,其输出P、N之间的相位一致性该怎么测试呢?

如何解决数据库与缓存一致性

自主驾驶系统将使用缓存一致性互连IP和非一致性互连IP

自主驾驶系统将使用缓存一致性互连IP和非一致性互连IP

评论