"有些信号虽然您不需要,但经常会进入系统中;这些信号称为“噪声”,我们必须了解并处理好噪声,才能成功地实现系统设计。这些噪声信号源于外部(“外部噪声”)和内部电路器件(“内部噪声”),它们具有各种特性,可以对它们进行计算并予以补偿。ADIsimPLL™是一款锁相环(PLL)电路设计和评估工具,可以协助用户评估和设计RF系统并对系统进行故障排除。该工具支持ADI公司的PLL频率合成器系列。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

锁相环

+关注

关注

35文章

550浏览量

87244 -

pll

+关注

关注

6文章

739浏览量

134569 -

RF

+关注

关注

65文章

3024浏览量

165637

发布评论请先 登录

相关推荐

AD9779内部锁相环无法锁定怎么解决?

外部参考时钟为90MHz,需要的到一个110MHz的中频信号,因此使用AD9779内部锁相环,进行8倍插值处理。reg01配置为11001000,reg8配置为01111100,reg9配置为

发表于 12-04 08:29

硬件电路设计之锁相环电路设计

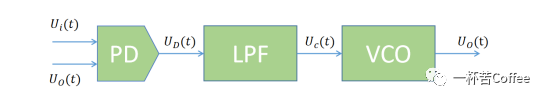

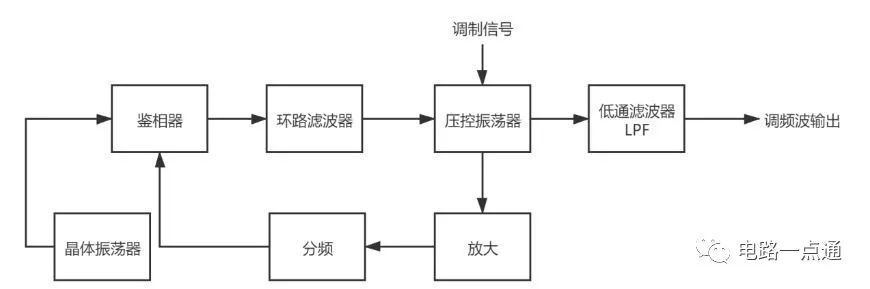

锁相环是一种 反馈系统 ,其中电压控制振荡器和相位比较器相互连接,使得振荡器频率(相位)可以准确跟踪施加的频率或相位调制信号的频率。锁相环可用来从固定的低频信号生成稳定的输出频率信号。首批锁相环

当锁相环无法锁定时,该怎么处理的呢?如何解决锁相环无法锁定?

当锁相环无法锁定时,该怎么处理的呢?如何解决锁相环无法锁定? 锁相环作为一种常见的电路设计,具有广泛的应用领域。然而,在一些情况下,由于种种原因,锁

锁相环是如何实现倍频的?

锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领域中。其中一个重要的应用就是

锁相环电路设计的解决方案 锁相环的基本构成和主要应用

锁相环接收一个它所锁定的信号,然后可以从其内部的VCO输出这个信号。乍一看,这可能不是特别有用,但是在你完全明白它,就有可能开发出大量的锁相环应用。

FPGA零基础学习之Vivado-锁相环使用教程

说,上货。

锁相环使用教程

锁相环是我们比较常用的IP核之一。PLL的英文全称是Phase locked loop即锁相环,是一种反馈电路。具有分频、倍频、相位偏移和占空比可调的功能

发表于 06-14 18:09

ADISimPLL锁相环电路设计和评估工具的应用

ADISimPLL锁相环电路设计和评估工具的应用

评论