声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

收发器

+关注

关注

10文章

3794浏览量

110574 -

模拟

+关注

关注

7文章

1445浏览量

85123 -

RF

+关注

关注

66文章

3196浏览量

171061

发布评论请先 登录

相关推荐

热点推荐

FMC子卡模块设计方案:FMC160-两路14位400Msps AD,两路16位400Msps DA FMC子卡模块

CameraLink图像模拟源, FMC子卡, FMC子卡模块, 万兆网络的触发采集, 中频信号采集

集中式ZDM-E0800V模拟量采集模块(上) — 基础应用

在工业自动化中,模拟量信号极为关键。致远电子的E系列高速IO模块ZDM-E0800V支持EtherCAT协议,可采集工业现场的电压模拟量信号。本文将详细

软件无线电-AD9361 璞致 PZSDR 软件无线电系列板卡之PZ-FL9361(FMCOMMS3)使用说明

ADI-AD936X系列包含AD9361、AD9364和AD9363三款高性能射频收发器,支持70MHz-6GHz频段和200kHz-56MHz带宽,适用于多种通信标准。FMCOMMS3

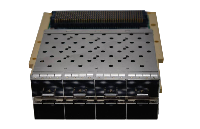

【FMC213】青翼凌云科技基于 VITA57.1 标准的 8 路 SFP+光纤通道数据传输 FMC 子卡模块

FMC213 是我司自主研制的一块基于 FMC 标准的 8 路万兆光纤 子卡模块。该板卡符合 VITA57.1 标准,该板卡可以作为一个理想的 IO模块耦合至FPGA前端,8路SFP+

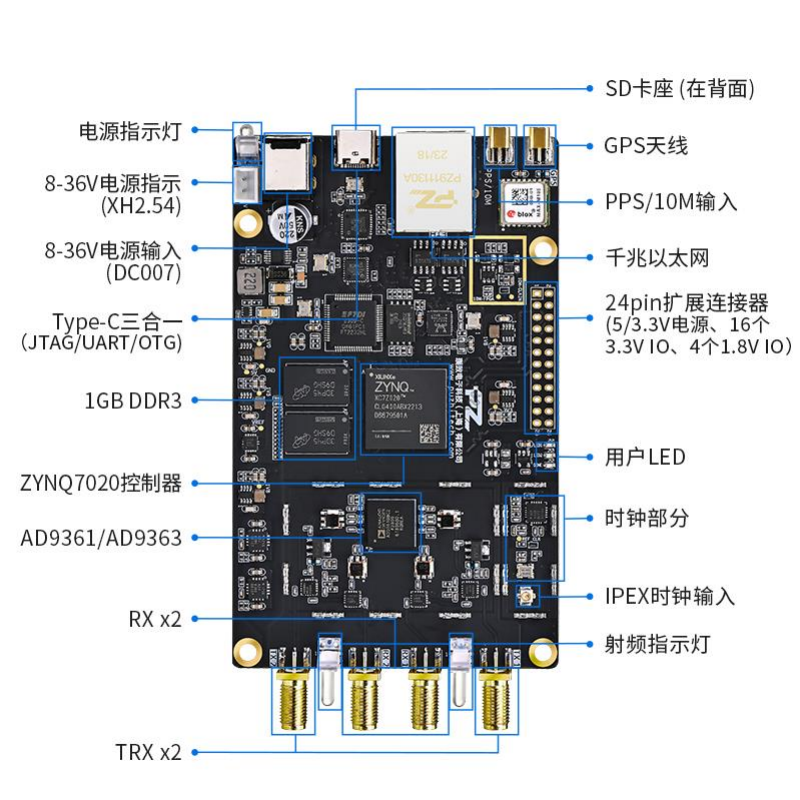

PZSDR 软件无线电 开发板系列板卡之P201Pro P203Pro 硬件说明—AD9361 AD9363

璞致PZSDR系列中的P201Pro/P203Pro板卡采用Xilinx ZYNQ7020主控搭配ADI AD9361/AD9363射频芯片(区别在于带宽),板卡提供三种供电方式(XH2.54

FMC子卡设计方案:FMC210-1路1Gsps AD、1路2.5Gsps DA的FMC子卡

FMC-1AD2DA是我司自主研发的一款1路1G AD采集、1路2.5G DA回放的FMC子卡。板卡采用标准FMC子卡架构,可方便的与其他FMC板卡实现

【PZSDR AD9361】——璞致PZ-FL9361 软件无线电模块:工业级射频解决方案的技术标杆

璞致电子推出PZ-FL9361软件无线电模块,搭载ADI AD9361射频芯片,实现70MHz-6GHz宽频覆盖与56MHz可调带宽,支持2T2R架构与工业级环境应用。模块兼容主流FP

AD9361

我使用AD9361芯片,参考时钟为10MHz,鉴相频率为20MHz,设置BBPLL频率为800MHz,ADC_CLOCK为BBPLL的2分频,为400MHz,clock_OUT为ADCclock的8

发表于 06-25 15:02

Why FPGA开发板喜欢FMC?

来都来了,我们就来好好讲讲为什么万能的FPGA如此青睐FMC?WhyFMC?FMC即FPGAMezzanineCard(FPGA中间层板卡),由子板模块和载卡两部分构成。FMC载卡:为

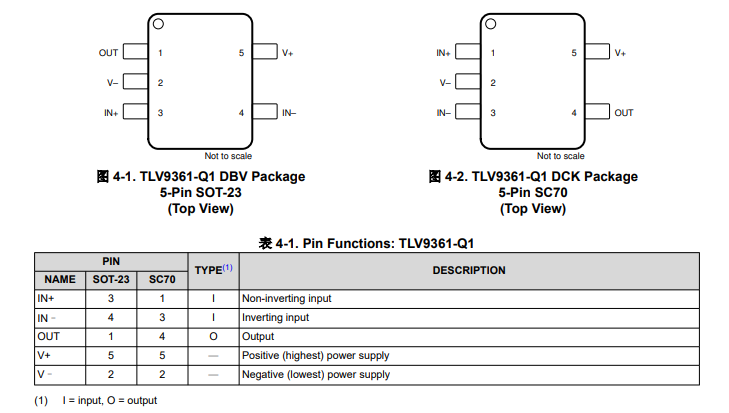

TLV9361-Q1 汽车类、单通道、40V、10.6MHz轨到轨输出运算放大器技术手册

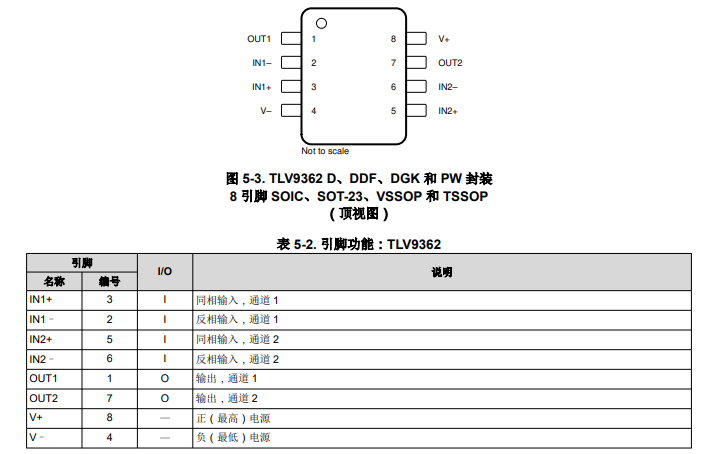

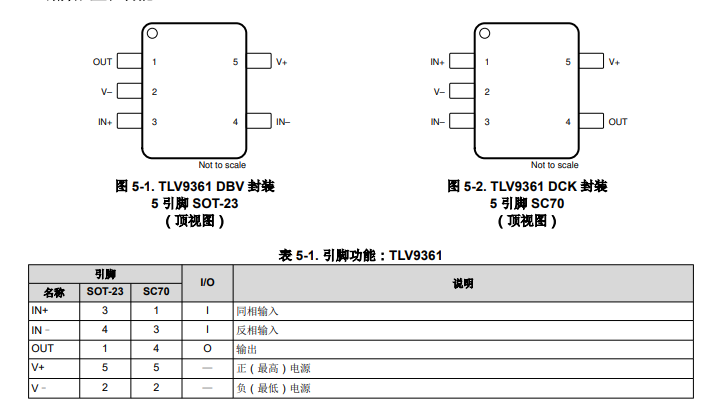

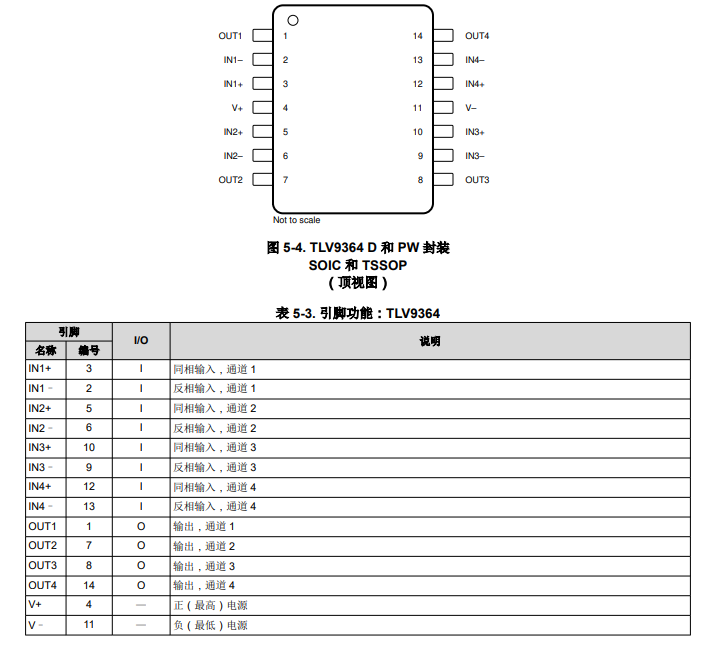

TLV936x-Q1 系列(TLV9361-Q1、TLV9362-Q1 和 TLV9364-Q1)是一个符合 AEC-Q100 汽车标准的 40V 成本优化型运算放大器系列。

FMC子卡设计方案:202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC7K325T的高速数据处理核心板

AD FMC子卡 , FMC子卡 , FMC子卡模块 , XC7K420T处理板 , 图像FMC子卡

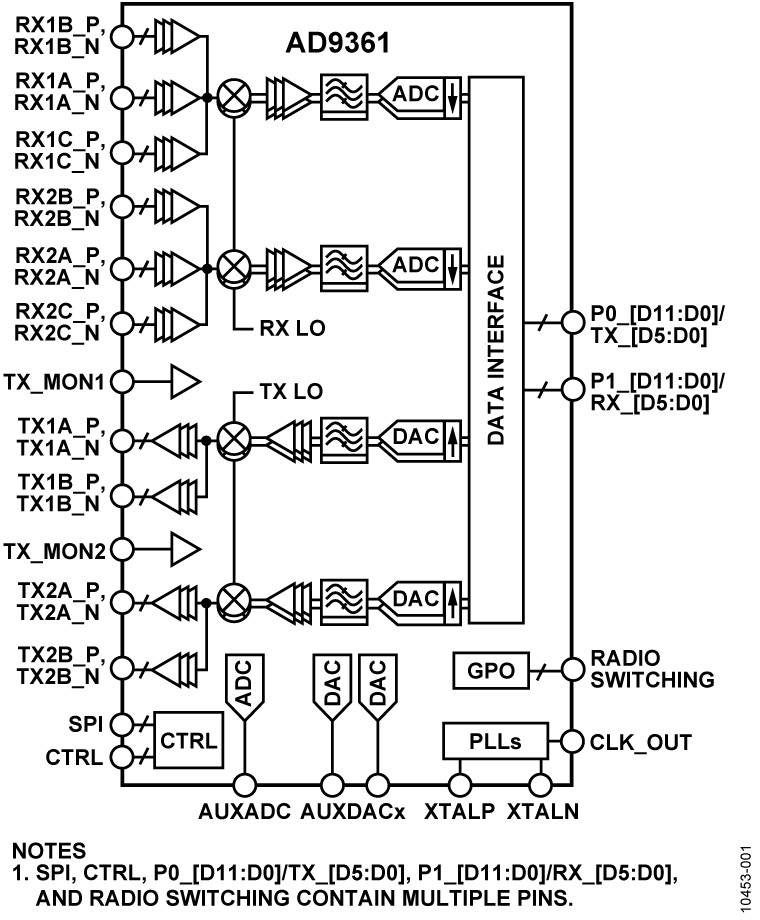

AD9361 RF捷变收发器,评估套件和开发资源

AD9361 *附件:AD9361_cn 中文数据手册.pdf 是一款面向3G和4G基站应用的高性能、高集成度的射频(RF)Agile Transceiver™捷变收发器。该器件的可编程性和宽带能力

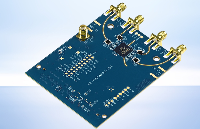

展示AD9361或AD9364性能的高速模拟FMC模块的介绍

展示AD9361或AD9364性能的高速模拟FMC模块的介绍

评论