整数N和小数N分频PLL合成器的相位噪声

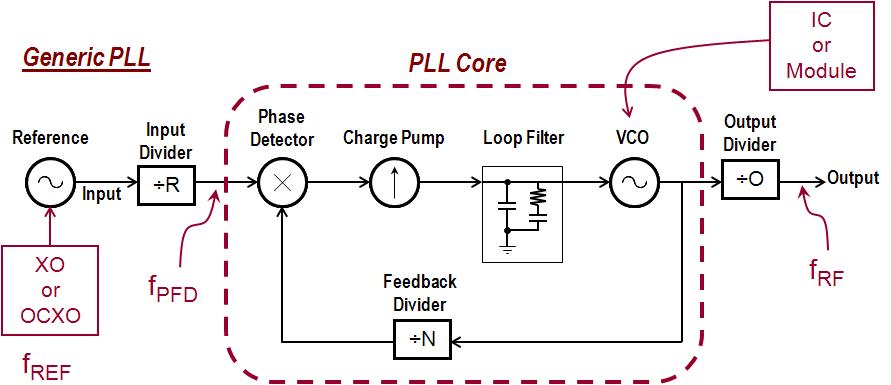

在产生高频,高线性度信号源时,低相位噪声至关重要。相位噪声是信号的不期望的变化或相位变化的量度。它在频域中测量并且等于时域中的抖动。使用PLL合成器时,总相位噪声由各种电路模块和元件的汇编组成,每个电路模块和元件都有助于最终值。各种贡献元件/电路包括压控振荡器(VCO),参考时钟和相关电路,相位频率检测器和各种内部缓冲器。

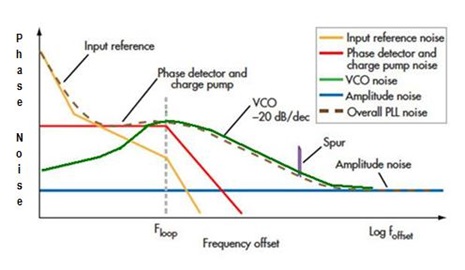

相位噪声可以分成每个元件/电路的贡献部分,包括参考噪声,相位频率检测器噪声,VCO噪声和宽带噪声(由于放大器/缓冲器和其他内部电路),它们建立了输出带隙相位噪声基底。

在决定整数N与小数N分频PLL合成器之间时,必须考虑整个相位的重要性噪声,成本,步长,PLL设计复杂度,寄生噪声(由分数N中的累加器或Δ西格玛引起的分数杂散),整数边界杂散(也是分数N效应)和参考杂散)以及环路锁定时间

小数N分频PLL的优点

分数N(frac-N)PLL合成器与整数N分频PLL相比具有几个关键优势,但在某些情况下,这些优势可能并不重要客户取决于应用程序。它允许更大的参考频率值,从而产生更小的乘数项N.由于PLL的相位噪声乘以所选的N值(f OUT = f REF * N)和frac-N PLL需要较小的N值,由于将参考频率乘以N而引起的相位噪声增加将减少20log(N)dB,但这部分地被相位频率检测器噪声的增加所抵消 - 10log (f PFD )dB(为简单起见,我们假设参考分频器值R为1,因此f REF = f PFD ;较大的整数值导致更多的噪音)。另一个优点是较小的步长或较高的分辨率。 frac-N允许步长为数十赫兹,而整数N可能产生数十千赫兹。与类似的整数N解相比,frac-N也会更快锁定。这是因为N的较低值允许更宽的环路滤波器带宽,这反过来允许更快的锁定时间。

Frac-N PLL的缺点

a的最大缺点frac-N PLL是它产生的分数和整数边界杂散,从使用角度来看它的复杂性增加(必须设计环路滤波器),并且在某些情况下成本更高。这些是客户可能选择整数N PLL的原因。 LTC的新型frac-N PLL器件减轻了这些缺点。它们被设计为产生非常低的整数边界杂散,并且它们的分数分频器使用先进的4阶ΔΣ调制器,其不产生分数杂散。关于复杂性,我们的FracNWizard软件具有先进的PLL设计和仿真功能,可简化回路设计工作。

检查数据表中的差异

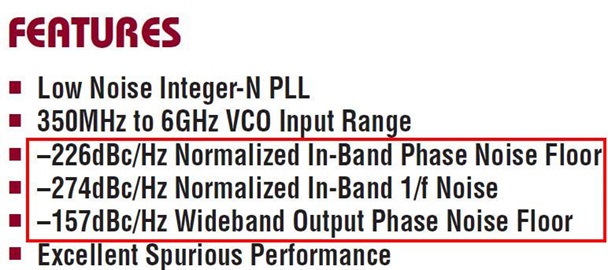

在检查整数N和压缩时N个数据表,可能会被一些相位噪声规范看起来相似的事实所困惑,即使frac-N据称具有较低的相位噪声。例如,查看LTC6947数据手册的首页,“特性”部分给出了三相噪声规范:归一化带内相位本底噪声,归一化1 / f噪声和宽带带外相位噪声基底。每个的值为-226dBc / Hz,-274dBc / Hz和-157dBc / Hz。对于LTC6945,数字为-226dBc / Hz,-274dBc / Hz和-157dBc / Hz。

关键是前两个规范是规范化的。这意味着它们的计算不需要考虑完成设计所需的其他电路元件,这使得工程师可以进行并排比较。但是,这并没有给出用户将获得的真实价值;相反,它是一个“品质因数”。当我们在实际应用中“非标准化”值时,PLL N分频器值和参考时钟频率是最终值中的因子。

归一化是Frac-N和整数N的原因可以有类似的价值观。当在典型应用中使用时,Frac-N通常会导致低得多的带内相位噪声,因为它通常允许更高的参考频率(或PFD频率),并且如前所述,这会产生较小的值。 N分频器(N),可降低整体相位噪声。

例如,对于具有100kHz频率步长和3GHz输出的LTC6945整数N分频PLL合成器解决方案,PFD设置为100kHz 。在使用LTF6947 frac-N PLL的相同示例中,PFD可以设置在更高的频率。我们选择50MHz。这导致最大频率误差为~100Hz(50MHz / 2 ^ 18)/ 2 - 除以2 ^ 18是因为LTC6947使用的18位Δ-Σ调制器,或者步长小1000倍。

继续这个例子,假设类似的归一化带内相位噪声值,frac-N 3GHz输出的带内相位噪声将比整数N低约27dB(见第21页) LTC6947数据手册图11为完整公式)。虽然LTC6947 frac-N PLL在frac-N模式下具有1dB更差的归一化带内相位噪声,但它提供比LTC6945整数N低26dB的带内相位本底噪声。

最后一点是因为相位本底噪声不依赖于杂散成分,所以frac-N和整数N-PLL都具有相似的值。

凌力尔特提供整数N(LTC6945 / LTC6946)和Frac-N(LTC6947 / LTC6948)PLL合成器。两种类型都具有出色的相位噪声性能如果需要较小的频率步长和最低的相位噪声,则Frac-N是最佳的。如果需要更低的成本和更低的复杂性,请选择整数N PLL。

-

振荡器

+关注

关注

28文章

3517浏览量

137635 -

合成器

+关注

关注

0文章

247浏览量

25130 -

pll

+关注

关注

6文章

740浏览量

134572

发布评论请先 登录

相关推荐

ADI发布相位噪声性能的PLL频率合成器ADF4153A

ADI推出4GHz PLL合成器具领先相位杂讯性能

超低噪声PLL时钟合成器AD9522-0/PCBZ

详解频率合成器高性能架构的实现

如何利用FPGA设计PLL频率合成器?

LTC6945 和 LTC6946:锁相环 (PLL) 频率合成器

CN0369 低相位噪声的转换锁相环频率合成器

pll频率合成器工作原理与pll频率合成器的原理图解释

两款具有优秀相位噪声性能组成的PLL合成器介绍

两款具有优秀相位噪声性能组成的PLL合成器介绍

评论