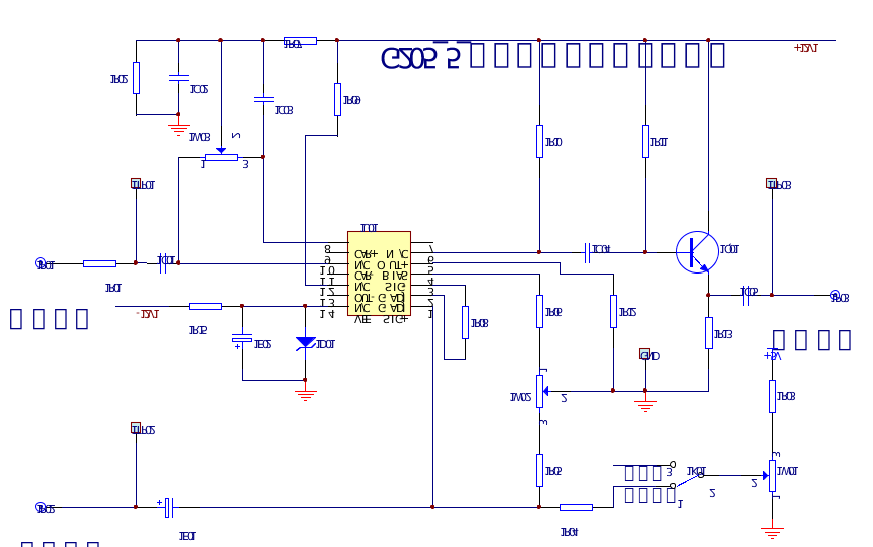

乘法器是众多数字系统中的基本模块。从原理上说它属于组合逻辑范畴:但从工程实际设计上来说,它往往会利用时序逻辑设计的方法来实现,属于时序逻辑的范畴。

通过这个实验使大家能够掌握利用FPGA/CPLD设计乘法器的思想,并且能够将我们设计的乘法器应用到实际工程中。乘法器的设计方法有两种:组合逻辑设计方法和时序逻辑设计方法。采用经合逻辑设计方法,电路事先将所有的乘积项全部计算出来,最后加法运算。采用时序逻辑设计方法,电路将部分已经得到的乘积结果右移,然后与乘积项相加并保存和值,反复迭代上述步骤直到计算出最终乘积。

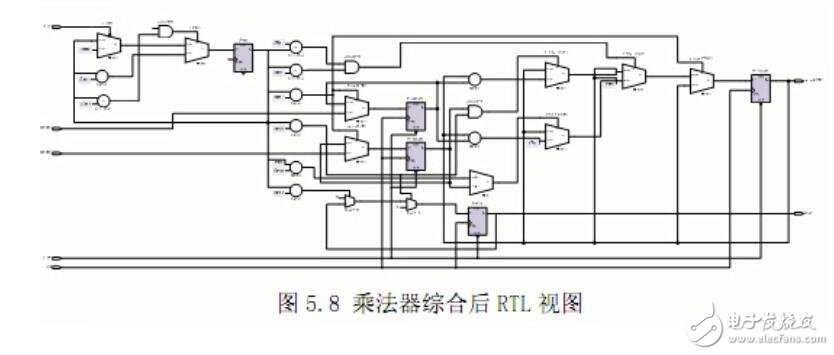

在该实验中就是要利用时序逻辑设计方法来设计-一个16位乘法器,既然是利用时序逻辑设计方法那么就得利用时钟信号控制乘法器运算。用时序逻辑设计方法与用组合逻辑设计方法比较,它有什么好处呢?利用时序逻辑设计方法可以使整体设计具备流水线结构的特征,能适用在各种实际工程设计中。

更多关于BJ-EPM240学习板之乘法器设计实验请看视频。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1599文章

21273浏览量

592820 -

乘法器

+关注

关注

8文章

189浏览量

36576

发布评论请先 登录

相关推荐

乘法器AD734上电后发热严重,数据漂移的原因?怎么解决?

乘法器AD734上电后发热比较严重,输入与地短接的情况下,输出数据不稳定,用数据卡采集可以看到明显的漂移,[size=13.3333px]采用的是芯片手册上的最基本的乘法电路,这种现象的原因是什么,是PCB设计的问题吗。

发表于 12-15 06:44

求助,关于二象限乘法器AD539的一些疑问

各位,请教乘法器的一些问题:

1.二象限乘法器AD539中控制通道Vx只能输入正信号,但是否只能为直流电平(用做电压控制放大器)?

2.如果控制通道Vx输入交流信号,理论上是否应该做偏置,使之在

发表于 11-22 07:48

用AD835乘法器做的一个电路,当X和Y的频率相同时,输出的波形问题求解

请教大神,我用AD835乘法器做的一个电路,当X和Y的频率相同时,相乘时输出是正弦波,但是当频率不相同时输出波形就会变为这种波形,请问有人知道是什么问题??谢谢!附件里有一张图是同频率相乘,波形是对的,另一张是不同频率相乘的图!

发表于 11-22 06:54

BJ-EPM240学习板之乘法器设计实验

BJ-EPM240学习板之乘法器设计实验

评论