1、使各种扬声器都工作在最合适的音频段

振膜尺寸和材料不同的扬声器,其最佳工作频带也不同。口径越大的扬声器,则低频特性就越好。所以,在其他条件相同时情况下,18英寸的低音效果肯定优于15英寸的低音效果就是这个道理。振膜材料的刚性和脆度越好、质量越轻,放音的高频特性就越好。很多高音扬声器采用钛膜或铟膜作为振膜材料,就是为了提高其高频特性;而低音扬声器的振膜一般采用纸、碳纤维、防弹布和橡皮(边)等材料,以利于低音再现。

使用分频器可以将高频信号送到高音扬声器中,低频信号送到低音扬声器中,高、低频信号各行其道,尽可能大地利用了各自扬声器的工作频带优势,以保证不同工作频段的扬声器充分发挥作用,使各频率的放音特性更加均衡一致。

2、不同频率声音扬声器振膜振动幅度不同所引起的切割失真

扬声器发音时,其振摸的低音振动幅度大、高音振动幅度小。从理论上讲,扬声器纸盆的振动幅度与再现声音频率的平方成反比,即同一扬声器振膜,在相同幅度的信号电压作用下,频率越低,振幅越大,也就是说,如果频率增加10倍,振幅将减少10的平方倍,即100倍。

如果我们用一只扬声器产生很宽频率范围的声音,由于振膜机械性能的限制,同时存在振幅非常宽的振动变化是非常困难的,这就必将发生声音切割失真的现象,使再现声音质量受到一定影响。研究发现,切割失真对低音的影响最大,当低音扬声器放送低音的同时,只要还有高音成分存在,就必然会导致切割失真,使低音出现发抖、发颤的现象。当然,高音扬声器出现切割失真也会使高音出现嘶哑的声音,只是影响没有低音大而已。

3、减少同一音箱中的不同扬声器之间产生的声音

干涉现象对于高、低音分离式音箱中的高音扬声器和低音扬声器来说,虽然它们的工作频段不同,但是如果将全频信号不加分频地送人高音扬声器和低音扬声器,肯定会出现高、低音扬声器同时发出相同声音的情况,当不同扬声器的相同声音相遇时,就很可能产生声波互相干涉现象有一点声学常识的人都知道,一旦出现声音干涉现象,就会出现梳状滤波效应、驻波等一系列问题,这些问题均会不同程度地影响声音的良好再现。

设置分频电路后,高音和低音扬声器分别获得自己最佳工作频段声音信号,它们之间发出声音的频率范围几乎不覆盖,除音箱分频点和分频交叉区域还会存在少量干涉外,其余频率声音的干涉现象根本就不再存在了。

分频点和分频交叉区域会存在声音干涉现象的原因很简单,由于分频器的分频衰减率不可能做得无穷大,在分频交叉区域,尤其是在分频点,高音扬声器和低音扬声器会同时存在对方频段的声音,这时出现声音干涉现象在所难免。所以说,分频器的分频衰减率做得越高,分频交叉区域就越小,扬声器问的声音干涉就越小。

-

扬声器

+关注

关注

29文章

1213浏览量

60138 -

分频器

+关注

关注

43文章

432浏览量

49298

发布评论请先 登录

相关推荐

分频器的作用 分频器的功率是不是越大越好

CAN时钟分频器在CANbus模块上不执行任何操作的原因?

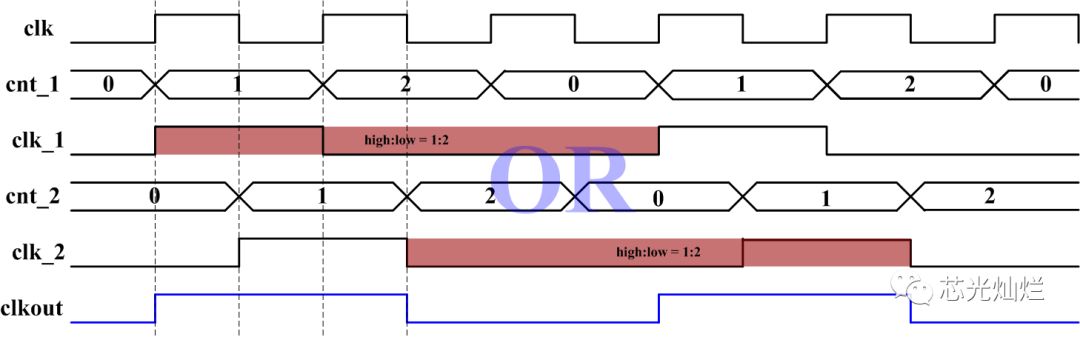

FPGA学习-分频器设计

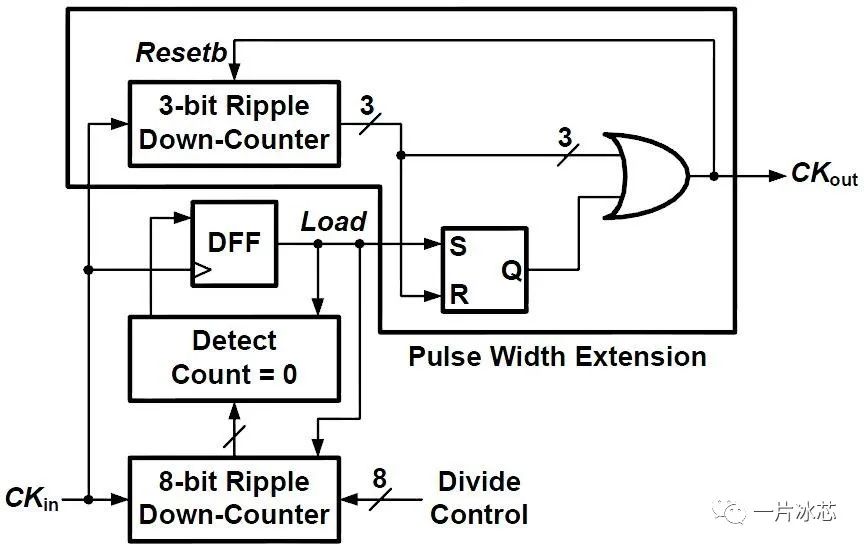

Sigma-Delta小数分频PLL中的分频器该怎么做?

分频器的常见用途

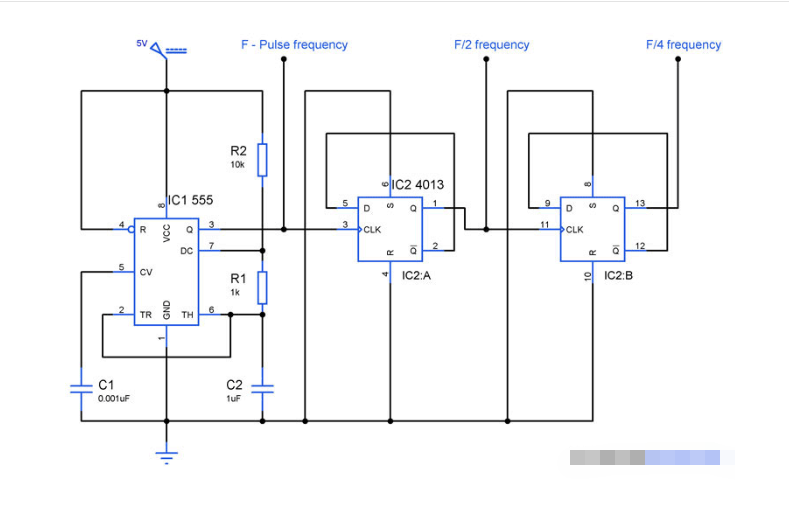

使用IC555和IC4013构建的分频器电路

029lan的pwm预分频器设置最少要为1吗,即2分频,设为0时没有输出是为什么?

音箱分频器有什么作用

音箱分频器有什么作用

评论