1、考虑中低单元指向性实用边界频率f=345/d(d=单元振膜有效直径)。通常8”单元的边界频率为2k,6.5”单元的边界频率为2.7k,5”单元为3.4k,4”单元为4.3k。也*是说使用上述单元,其分频点不能大于各单元所对应的实用边界频率。

2、从高音单元谐振频率考虑,分频点应大于三倍的谐振频率。也就是说从高音单元的角度出发,通常分频点应大于2.5k。

3、考虑中低音单元高端响应Fh,通常分频点不应大于1/2 Fh。 实际上,二分频音箱上述条件很难得到同时满足。这时设计者应在这三者中有一个比较好的折中选择。但必须强调的是,*个条件即实用边界频率应该优先满足。

4、三分频的情况下,通常应将两个分频点隔得愈远(应在三个倍频程以上),组合后的系统响应会变得愈好。否则,将会出现复杂的干扰辐射现象。

5、低音与中音的分频点应考虑人声声像定位的问题。应使人声的重放尽可能由中音单元来承担,以避免人声的声像定位音色发生过大的变化。这一点往往容易被设计者所忽视。通常这一分频点应为200-300Hz。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

音箱

+关注

关注

36文章

624浏览量

67090 -

分频点

+关注

关注

5文章

7浏览量

7729

发布评论请先 登录

相关推荐

分频器的作用 分频器的功率是不是越大越好

分频器是一种电子设备,用于将输入信号分成不同频率的输出信号。其主要作用是将原始输入信号分离成多个频率范围内的信号,以供不同的电路进行处理。分频器广泛应用于通信、测量和音频系统中。 分频器的主要

CAN时钟分频器在CANbus模块上不执行任何操作的原因?

。

CANCLKCON(CAN时钟控制寄存器)中还有CANCLKDIV(CAN时钟分频器选择位),其范围为1 - 128。

据我所知,CANCLKDIV 什么也没做。我只使用普通的 CAN,而不是 CAN-FD

发表于 01-22 06:36

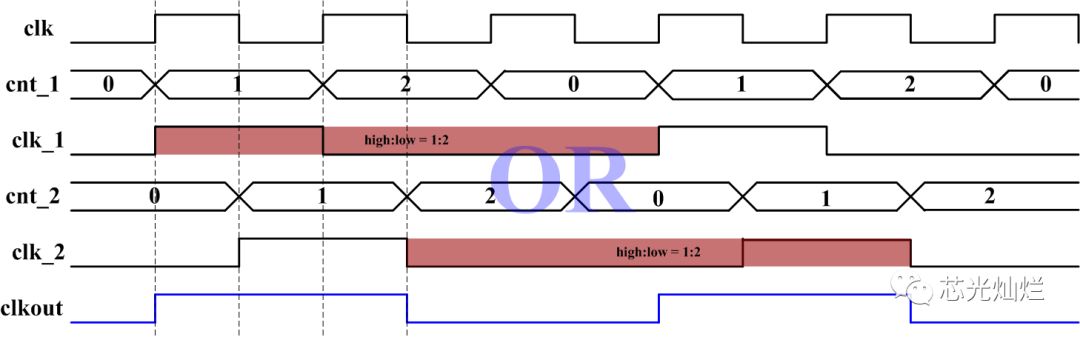

FPGA学习-分频器设计

分频器设计 一:分频器概念 板载时钟往往 是 有限个( 50MHZ/100MHZ/24MHZ/60MHZ… ),如果在设计中需要其他时钟时,板载时钟不满足时,需要对板载时钟进行分频 / 倍频,目的

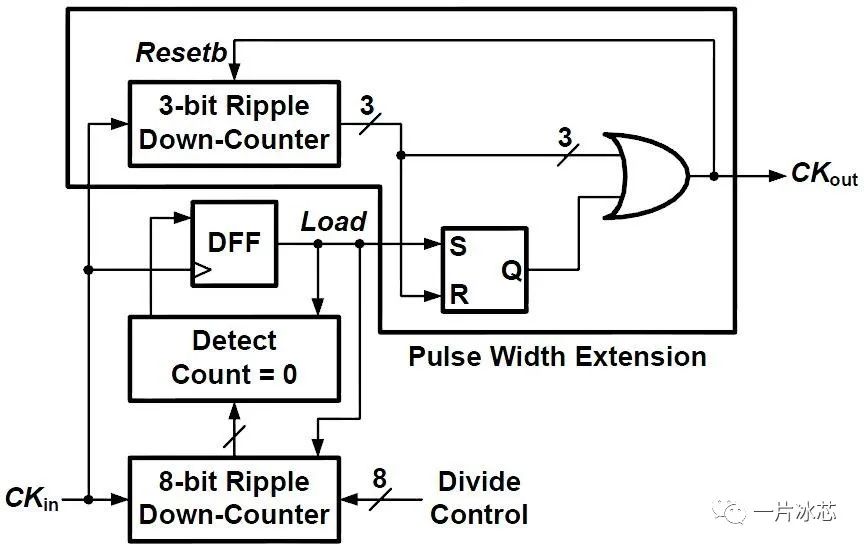

Sigma-Delta小数分频PLL中的分频器该怎么做?

文献给出的分频器结构如图1所示。该分频器最高输入频率(f~in~)为16.3GHz,也就是一个周期只有(T~in~,T ~in~ = 1/ f~in~)61.3ps。

分频器的常见用途

分频器是一种电子设备,其主要作用是将输入信号的频率降低到较低的频率。它通过将输入信号分为若干个等分的周期,每个周期输出一个脉冲或波形,从而实现对输入信号频率的降低。

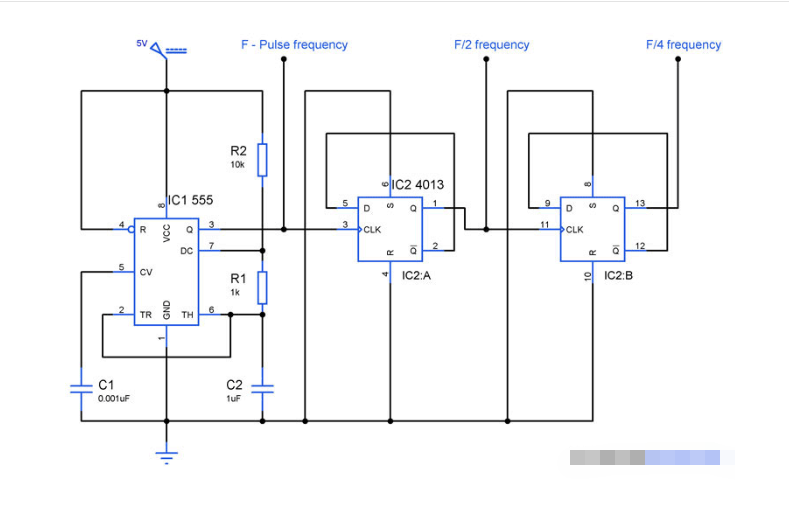

使用IC555和IC4013构建的分频器电路

曾经遇到过这样一种情况,即您只有一个特定频率的信号源,需要获取多个频率的信号。如果是,这种电路可能是您需要在设计中使用的电路。上述电路是一个分频器,能够通过一定的因素对输入时钟频率进行分频。该分频器

029lan的pwm预分频器设置最少要为1吗,即2分频,设为0时没有输出是为什么?

如题,这样一来,pwm的时钟哪怕是来自HCLK(029不支持PLL作为pwm时钟)最高50MHZ,经预分频器最少2分频的话,时钟最高只有25Mhz了?M0518pwm的预分频器可以设为0,不分

发表于 06-19 08:14

请叫大神帮我画出分频器电路图

买了一个国产某jbl品牌的音箱,感觉唱歌声音发闷,不好听。分频器照片在这,拜托,谁能帮我画出电路图,我分析一下,红色白色蓝色黑色一边的4颗线接4个高音喇叭的,看起来这4个喇叭一样,但是说明书上面说

发表于 06-01 22:41

音箱分频器分频点选择

音箱分频器分频点选择

评论