IC产业的进步取决于IC制造商继续提供更多性能和功能的能力。随着主流CMOS工艺在理论,实践和经济方面的限制,降低IC成本(基于每个功能或每个性能)比以往任何时候都更具挑战性和挑战性。2019年版IC Insights的McClean报告(500页),有关集成电路行业的完整分析和预测(2019年1月发布)表明,公司提供的面向逻辑的工艺技术比以往任何时候都多。

图1列出了公司目前使用的几种领先的高级逻辑技术。主要节点之间的每个过程生成的衍生版本已成为常规事件。

英特尔- 其2018年末推出的第九代处理器的代号为“Coffee Lake-S”,有时也称为“Coffee Lake Refresh”。英特尔称这些处理器是新一代产品,但它们似乎更多增强了第八代产品。细节很少,但这些处理器似乎是在14nm ++工艺的增强版本上制造的,或者可能被认为是14nm +++工艺。

使用其10nm工艺的大规模生产将在2019年推出,它将于2018年12月推出新的“Sunny Cove”系列处理器。看起来Sunny Cove架构基本上取代了应该是10nm的Cannon Lake架构。预计到2020年发布,当然10nm +衍生工艺将进入批量生产阶段。

台积电- 台积电的10nm finFET工艺于2016年底投入批量生产,但已从10纳米迅速发展至7纳米。台积电相信7nm产品将成为28nm和16nm等长寿命节点。

台积电5纳米工艺正在开发中,预计将于2019年上半年进入风险生产阶段,到2020年将开始量产。该工艺将使用EUV,但它不会是台积电利用EUV技术的第一个流程。首先是该公司7nm技术的改进版本。N7 +工艺仅在关键层(四层)上使用EUV,而N5工艺将广泛使用EUV(最多14层)。N7 +计划于2019年第二季度投入量产。

三星- 在2018年初,三星开始批量生产第二代10nm工艺,称为10LPP(低功率+)。在2018年晚些时候,三星推出了第三代10nm工艺,称为10LPU(低功耗终极),提供了另一项性能提升。三星采用10nm的三重图案光刻技术。与台积电不同,三星认为其10纳米工艺系列(包括8纳米衍生产品)的生命周期很长。

三星的7nm技术于2018年10月投入风险生产。该公司不再提供采用浸没式光刻技术的7nm工艺,而是决定直接采用基于EUV的7nm工艺。该公司正在将EUV用于7nm的8-10层。

GlobalFoundries- GF将其22nm FD-SOI工艺视为其市场,并与其14nm finFET技术相辅相成。该公司称22FDX平台的性能与finFET非常接近,但制造成本与28nm技术相同。

2018年8月,GlobalFoundries宣布将停止7nm开发,因为该技术节点的生产成本增加,并且因为有太少的代工客户计划使用下一代工艺,因此对战略进行了重大转变。因此,该公司转向其研发工作,以进一步增强其14nm和12nm finFET工艺及其完全耗尽的SOI技术。

五十年来,集成电路技术的生产率和性能得到了惊人的改善。虽然该行业已经克服了摆在它面前的许多障碍,但似乎障碍仍在不断扩大。尽管如此,IC设计人员和制造商正在开发比增加芯片功能更具革命性的解决方案。

-

CMOS

+关注

关注

58文章

5146浏览量

233315 -

IC

+关注

关注

35文章

5540浏览量

173183

原文标题:逻辑IC在工艺技术的进步

文章出处:【微信号:TopStorage,微信公众号:存储加速器】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

什么是BCD工艺?BCD工艺与CMOS工艺对比

是德科技携手Intel Foundry成功验证支持Intel 18A工艺技术的电磁仿真软件

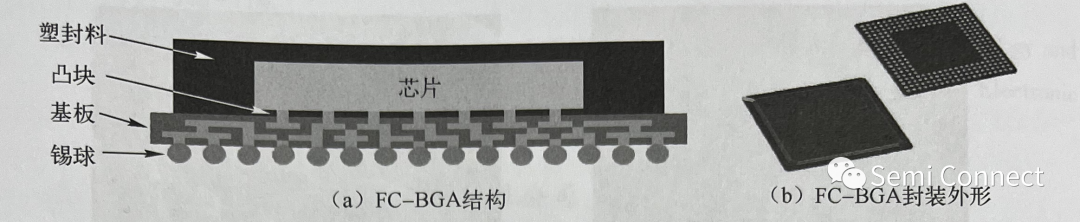

MEMS封装中的封帽工艺技术

MEMS和硅光集成工艺成果入选《2023年上海科技进步报告》

三星与Arm携手,运用GAA工艺技术提升下一代Cortex-X CPU性能

电路板改板技术之光板测试工艺指导

1天工艺技术培训、1天技术产业报告分享,凝聚先进封测奋进力量!

晶圆临时键合及解键合工艺技术介绍

高密度小间距LED显示屏工艺技术解析

Cadence定制设计迁移流程加快台积电N3E和N2工艺技术的采用速度

CMOS逻辑IC基础知识:解密组合逻辑背后的强大用途(上)

逻辑IC在工艺技术的进步的体现

逻辑IC在工艺技术的进步的体现

评论