如果时序定义明确且时间关键功能被分区,单核微控制器可以执行多任务,以便中断和定时器服务例程响应时间足够快,可以处理手头的任务。然而,它的设计相当于杂耍。当一个球在空中不需要服务时,另一个球可能需要立即服务以保持过程移动。只要你足够快以切换上下文,一切都很好。

当任务重叠时,可能无法足够快地做出反应,例如当同时发生多个同步和异步刺激时。在这些情况下,只有几个选项。一个是更快的处理器。另一种方法是使用多个处理器并将应用程序划分为时间可管理或流水线组块。第三种,也是最好的选择,就是采用单芯片双核或多核处理器。

本文介绍具有多个核心的处理器。这些部分允许任务主管为每个核心分配个人职责,以便其他干扰不会影响完成诸如时间关键控制循环等任务所需的实时性能。

总线背面

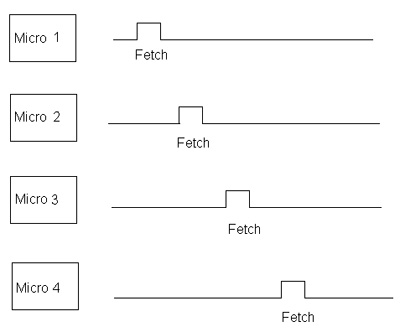

了解如何最好地选择双核或多核处理器的关键在于它如何使用或复制资源。最简单(也是非常有效)的方法是每个处理核心都有自己的“支持人员”,包括自己的程序和数据存储器,时钟和I/O.共享外设需要由当前使用它们的处理器内核声明(图1),双端口内存可以作为交换关键数据的手段。

图1:当每个微核心拥有自己的资源以便独立运行时,提供最大的自由度。唯一可能的争用点是必须设计用于处理它的双端口RAM。

共享资源可以节省芯片面积和功耗,但必须以每个处理器内核始终可用的方式进行同步。浮点处理器可能需要多个指令和周期来加载操作数,然后进行处理和存储。在目前为止讨论的两种情况下,在资源空闲之前将不同的核心保持在等待状态并不是一种有效的方法,并且在这些条件下或多或少会将性能降低到单核级别。

对于像数据总线这样的通用数据路径资源也是如此。如果内部只有一个数据总线,则每个核心都需要访问它,通常每个周期至少有一次,但有时更多。存在争用时可以插入等待状态,但这对原因没有帮助。

正如您所猜测的那样,内核的同步性和时序性是一个重要因素。如果每个内核以其自己的频率以自己的频率运行,则可以访问共享总线。但是,如果使用公共时钟在内核之间交错微状态,则可以在没有任何争用的情况下最大限度地利用内部资源。以Von Neumann架构为例,我们可以让四个核心处理器使用读取,解码,操作和执行周期共享一个公共总线(图2)。请注意,虽然第2阶段和第3阶段操作可以在每个处理器内部,但使用总线的执行周期(如内存存储)仍然可能导致争用。如果I/O路径对处理器是唯一的,则可以在执行周期期间执行一些I/O操作。

图2:当多个微控制器及时交错时,更容易实现对总线管理等公共资源的更好控制。当发生内存和I/O读写时,仍然必须小心,因为它们可以声明总线。具有分割代码和数据总线的哈佛架构可以解决这个问题。

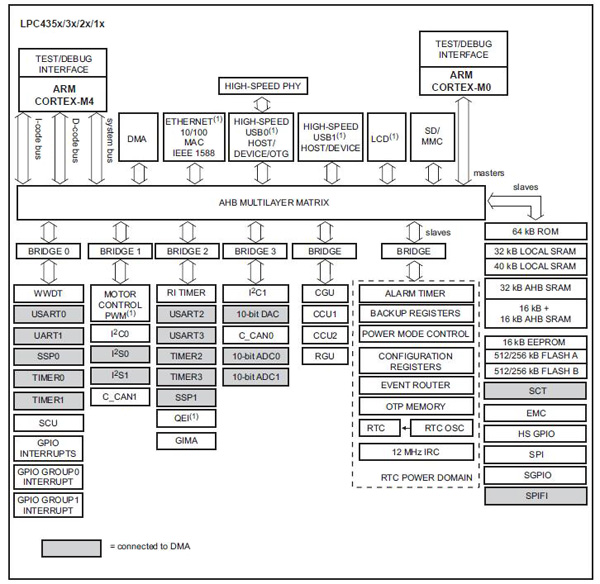

要记住的另一个因素是部件中的每个核心处理器不必相同或相同。恩智浦半导体的32位非对称双核204 MHz PC4337JBD144E是该公司LPC43xx系列ARM®Cortex™M4和M0内核的成员,采用单封装。这些部件的ROM,RAM,外设组合,I/O和封装尺寸各不相同,但所有部件都具有较小的M0内核,可以接管内务管理,初始化和数据管理工作,而M4内核可以自由地执行更多过程密集型功能,得益于其浮点硬件和DSP扩展。

恩智浦部件使用多层矩阵和各个外设桥来解决处理器内核和外设之间的仲裁问题(图3)。 Master和Slave指定也确保优先级。其思想是AHB矩阵将ARM Cortex M4总线和其他总线主控器连接到外设,以便允许不同总线主控器同时访问位于不同从端口上的外设。

图3:为解决总线争用问题,恩智浦使用AHB矩阵,允许多个内核和外设在需要时访问总线。

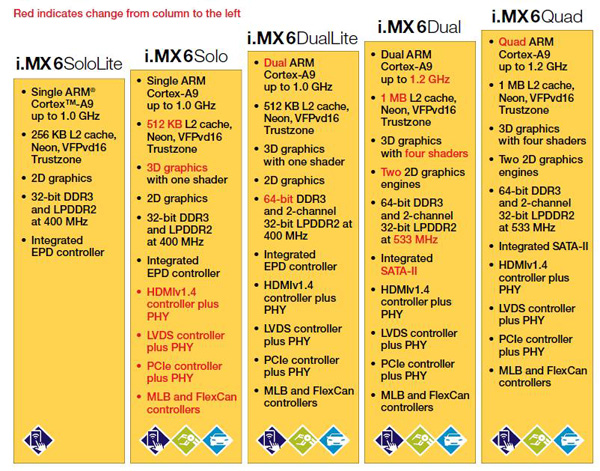

飞思卡尔的i.MX 6是一系列可扩展的单核,双核和四核32位ARM 9处理器。它们的内核每个时钟速度为1 GHz,与其他高端处理器一样,这些器件具有硬件支持,如USB(和OTG),以太网,MMC/SD卡,PCI,2D和3D图形以及SATA等外设。只是几个(图4)。

图4:飞思卡尔的方法是在添加核心时添加更复杂的外围设备和接口。这允许使用内核代码进行可扩展开发以进行基本固件验因此,在逐步添加更多核心和功能之前,可以建立稳定的固件库。

采用飞思卡尔的双核MCIMX6D5EYM10AC采用624引脚FBGA封装。它的0.9至1.5 V操作可将热量和功耗降至最低,而224 I/O并非易事。虽然这个I/O的一部分通过外部总线接口专用于外部程序存储器,但这些部件非常密集,晶体管数量非常高,因此保持低功耗至关重要。

应该注意,这些核不是不对称的。它们实际上完全相同。这意味着单核设计可以迁移到双核或四核设计,并且随着性能的提高,代码将兼容。这可能是一个关键的决定因素,特别是如果您正在设计笔记本电脑,智能手机,笔记本电脑或其他需要同时支持许多高端外设的多功能设备。

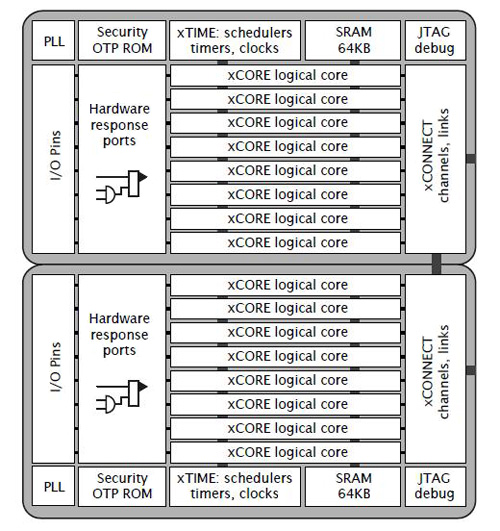

多核MCU领域的另一个参与者是XMOS,它提供了一系列可扩展的32位部分。 XS1系列包括单核,双核,四核,十六进制和八核,以及多达16核的器件,从48引脚TQFP封装到512引脚LFBGA封装(图5)。这些部件还包含丰富的外围设备和功能。考虑0.95至3.6 V 48引脚400 MIPS四核XS1-L4A-64-TQ48-C4。每个核心(称为磁贴)可同时执行实时任务,并可执行计算,高级DSP代码,控制代码或处理I/O的软件。

图5:借助XMOS的通道链接和响应端口映射方法,最多可将16个内核放在一个封装中。当扩展发生时,可以复制ROM,RAM和时序等关键功能。

在XMOS中,部件调度硬件执行类似RTOS的功能,以确保低延迟并消除中断,确保确定性操作。由于每个核心都是相同的,随着计算和多任务处理需求的增长,您的设计功能也可以增长,而无需重新开始创建软件。

总之,处理器和功能的巧妙划分可以简化设计,多核部件可以成为帮助工程师解决关键实时需求的关键因素。许多精心设计的零件和工具随时可以提供帮助。有关本文中讨论的部分的更多信息,请使用提供的链接访问Digi-

-

微控制器

+关注

关注

48文章

6806浏览量

147601 -

处理器

+关注

关注

68文章

18250浏览量

222055 -

存储器

+关注

关注

38文章

7141浏览量

161971

发布评论请先 登录

相关推荐

多核处理器实时控制性能的介绍

多核处理器实时控制性能的介绍

评论