锁相环是最通用的电路功能之一。它们用于为处理器提供时钟(相当良好的情况),以及用于在固定和调谐频率发送器和接收器中建立调谐。

然而,最困难的挑战之一是在无线链路中恢复,清理和重新计时定时信号。与处理器时钟不同,此处通道的时钟信号不是显式或单独的信号,而是嵌入在已调制的数据流中。即使发送和接收时钟都是完美的并且也完美同步(从未出现过这种情况),该通道将具有噪声,衰减,变化的SNR,失真以及许多其他腐蚀因素。

除了在无线信道中使用外,PLL在有线和光纤链路中起着类似的作用。在后两种情况下,与无线相比,接收信号通常较少损坏且更稳定,因此稍微简化了任务,但数据速率通常要高得多(某些光链路的数十Gbps),这加剧了挑战。因此,PLL必须克服不同的困难,具体取决于通道介质。

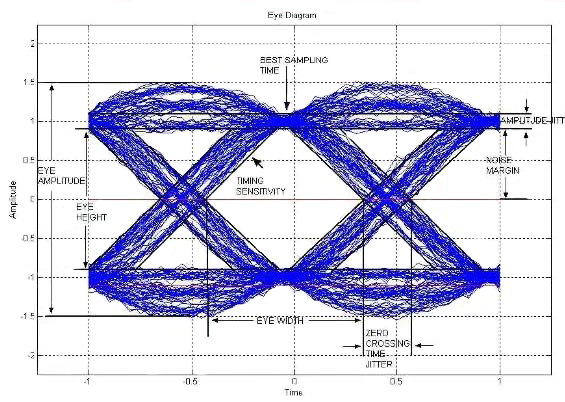

时钟恢复挑战的复杂性在与通信通道相关的最有用图表中清晰显示,眼图(图1) 1 。该图实时覆盖了所有接收到的数据流位,从而构建了一个复合数据,显示接收器的定时抖动,失真和衰减程度。

图1:使用恢复的系统时钟覆盖所有接收数据位的眼图,揭示了有关抖动,衰减,失真的大量信息和它所代表的“理想”数字信号相比,接收信号的许多其他特性。 (由Yellow Fourier Technologies Private Ltd.提供)

虽然理想的数据位看起来像方波,但任何实际位都具有非垂直斜率和圆角作为其最小缺陷;此外,实际接收信号将具有各种抖动,失真和衰减。由于信道限制,比特在时间上延伸,它们重叠,结果是符号间干扰(ISI),这使得更难以实现低误码率(BER)。

因此,接收机尽管存在许多破坏因素,但必须从接收的调制数据流中提取数据时钟的定时。形式上,此功能称为“时钟和数据恢复”或“时钟和数据重定时”(CDR),但通常用俚语“时钟清理”来描述。接收器电路使用此恢复的时序来确定最佳时刻到对数据进行抽样。目标是在接收的比特值上实现较低的误码率。

PLL

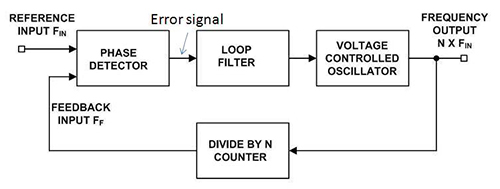

PLL使用闭环负反馈拓扑将接收信号的嵌入式时钟与标准的本地生成时钟相匹配(图2)。 PLL的原理和操作已经在技术文章,书籍和网站中得到了广泛的介绍,解释主要是口头的,直观的方法,一直到那些提供强大的数学分析的方法 2,3 (PLL对于这种水平的调查来说,它是一个很好的候选者,因为它可以准确地建模)。虽然PLL多年来都是全模拟电路,但现在它们通常采用数字电路实现(例如,模拟VCO被数控振荡器取代);在更高的频率下,模拟仍然是唯一可行的选择。

图2:基本PLL是一种闭环,负反馈设计,可以比较本地生成的相位/频率与接收信号的相位/频率,并通过滤波后的误差信号调整VCO以跟踪输入信号。

在所有PLL应用中,环路滤波器的细节对于证明所需的整体性能。当然,主滤波器参数是带宽,其次是诸如阻尼,滚降陡度,通带纹波和带外衰减等因素。

较窄的带宽将导致恢复的时钟输出抖动减少,这是一件好事。然而,这个相同的窄带宽意味着它将花费更长的时间来初始获取接收信号并在该信号经历频率变化时将其锁定。在无线链路中,这些频移通常是由于多径,失真,传播延迟问题,甚至是多普勒效应(即使在地面速度下也很重要 - 想想雷达速度枪)。

无线链接也面临着更多挑战。对于有线和光学链路,端点和介质通常固定在适当的位置,因此许多腐蚀影响是相对静止的;对于无线链路,一个或两个端点可能正在移动并且信道本身正在改变,因此接收信号实时地经历许多变化。因此,环路滤波器必须针对动态环境进行设计,超出噪声和衰减等标准问题。

显然,用于高速无线链路的PLL及其滤波器的参数最初是针对最可能的信道条件设置的。对于非常困难的情况的设计有时不使用单个固定滤波器,而是使用具有时间常数的更高级的滤波器和可以“动态”动态调整以匹配条件的其他参数。

与目标应用匹配的CDR IC

对于许多无线应用 - 尤其是Wi-Fi节点等大众市场消费类应用 - CDR PLL嵌入在更大的IC中整个前端功能(尽管接收通道LNA [低噪声放大器]和发射通道功率放大器[PA]通常是独立的分立器件)。但是,用于高速链路的CDR PLL通常是独立的,功能有限的设备,以满足其性能要求

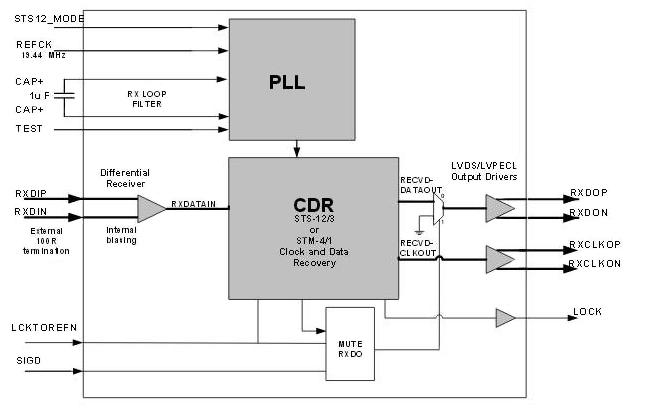

Exar XRT91L33就是这样一个例子(图3)。该IC设计用于SONET/SDH 622.08 Mbps STS-12/STM-4或155.52 Mbps STS-3/STM-1应用,并通过将其片上压控振荡器与输入串行非返回同步来实现CDR功能到零(NRZ)数据流。 PLL在启动时锁定到本地参考时钟。一旦实现锁定,它就会尝试锁定传入的数据流。

图3:Exar用于SONET/SDH的XRT91L33 622.08 Mbps STS-12/STM-4或155.52 Mbps STS-3/STM-1应用程序提供时钟数据和恢复,并且在信号丢失或由于任何原因无法实现锁定的情况下也具有“后退”位置。

认识到可能存在信号丢失的时段,无论何时恢复的时钟频率偏离本地参考时钟频率超过约±500 ppm,时钟恢复功能切换到本地参考时钟,断定失锁,并将LOCK输出引脚拉至低电平状态。用户为这款3.3 V,20引脚TSSOP器件提供外部滤波电容,以满足预期情况。

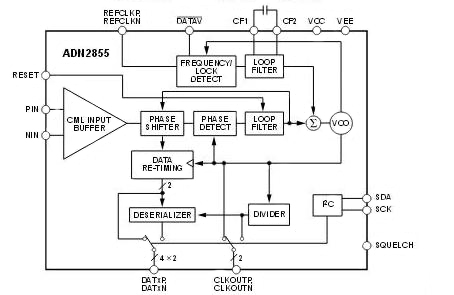

另一个例子是ADN2855,这是ADI公司的突发模式时钟和数据恢复IC它可以在155.52 Mbps,622.08 Mbps,1244.16 Mbps或1250.00 Mbps数据速率下运行(可通过I 2 C接口选择)。如图4所示,它专为GPON/BPON/GEPON光线路终端(OLT)接收器应用而设计。 ADN2855需要一个锁定到输入数据频率的参考时钟;在操作中,IC的环路相对于该参考时钟获得频率锁定,将VCO拉向0-ppm频率误差。与Exar部分一样,环路滤波器电容由用户提供,标称值为0.47μF。

图4:ADN2855, ADI公司的突发模式时钟和数据恢复IC可以运行高达1250.00 Mbps的数据速率;用户提供的滤波电容的标称值为0.47μF。

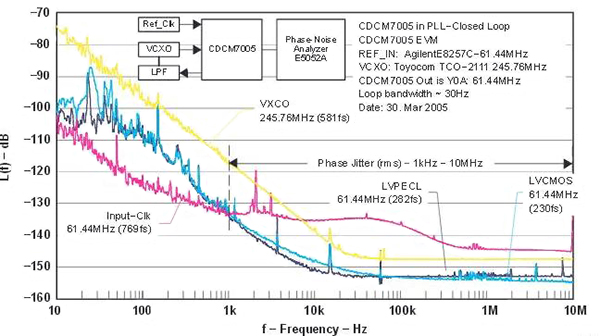

德州仪器公司的CDCM7005针对不同类别的应用,具有耐辐射性(版本CDCM7005-SP),低相位噪声和低偏移时钟同步器和抖动清除器,将压控晶体振荡器(VCXO)频率与两个参考时钟之一同步; VCXO时钟工作频率高达2 GHz。坚固耐用的IC经过50 kRad(Si)TID认证,QML-V符合SMD 5962-07230标准,可在整个军用温度范围(-55°C至125°C Tcase)下运行。

通过选择外部VC(X)O和环路滤波器组件,可以调整PLL环路带宽和阻尼系数,以满足不同的系统要求。在10 kHz和10 MHz之间的频率下,相位噪声低于140 dB(图5)。有两个PLL锁定指示:数字锁定信号或模拟锁定信号。两个信号都指示PLL是否根据用户选择的锁定条件达到或失去锁定。与ADI公司的PLL一样,许多工作参数都是通过串行总线用户设置的;这里是SPI总线。

图5:德州仪器(TI)的CDCM7005-SP是一款耐辐射PLL,可将压控晶体振荡器(VCXO)频率与两个参考频率之一同步时钟,工作频率高达2 GHz。

-

处理器

+关注

关注

68文章

18257浏览量

222079 -

振荡器

+关注

关注

28文章

3515浏览量

137632 -

发送器

+关注

关注

1文章

237浏览量

26549

发布评论请先 登录

相关推荐

利用PLL清除无线链路中的时钟信号

利用PLL清除无线链路中的时钟信号

评论