虽然通常认为噪声等随机信号是一个问题,但通信和设备测试之类的应用却依赖于随机位序列和噪声的独特特性。然而,对于预算紧张的设计人员或一次性测试而言,购买专用的伪随机二进制序列 (PRBS) 或任意波形发生器可能并不可行。在这种情况下,使用现成的 CMOS 器件来构建一个则更具成本效益。

本文将描述 PRBS 和噪声在电子学中的有用角色,然后介绍现成的 CMOS IC,并展示如何使用它们来生成所需的伪随机噪声和二进制序列。

“良好”噪音的角色

随机白噪声在频域中具有平坦的频谱。白噪声源激励的放大器或滤波器的平均输出幅度频谱将提供该设备的幅度频率响应。

在通信中,CDMA 发射器的数据流通过伪随机二进制序列 (PRBS) 多路化。然后,它可以作为多路其他信号使用相同的射频通道传输。在接收器端将复合信号与相同的 PRBS 相关联,将提取干扰很小或没有干扰的原始数据流。鉴于这些随机信号非常实用,因此能够视需要生成它们是很重要的。

生成 PRBS

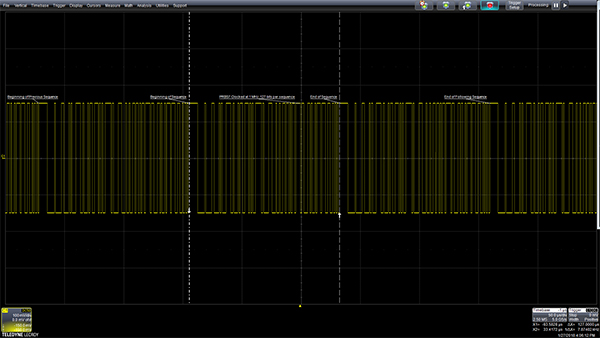

PRBS 是一个周期性的确定性信号,由一系列数字 1 和 0 组成。1 级或 0 级的持续时间是 PRBS 发生器的时钟周期的倍数。在发生器的模式重复周期内,1 和 0 的模式是随机的(图 1)。

图 1:PRBS7 信号是 7 位长度的 PRBS 测试信号,其周期为 27 -1 或 127 位。该信号的时钟频率为 1 MHz,周期为 127 ms,由示波器光标标记。(图片来源:Digi-Key Electronics)

图 1 中的信号是由一个 7 级发生器产生的 PRBS7 测试信号,其在每个模式周期内包含 127 位。在每个周期内,位模式是随机的,但整个序列每 127 个时钟周期重复一次。

这些测试信号可以在软件或硬件中生成。用于测试的硬件实施的优点在于可在外部获得信号以驱动被测设备。

线性反馈移位寄存器

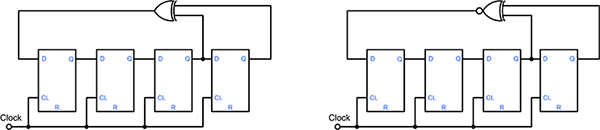

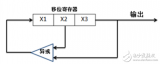

PRBS 的硬件实施使用线性反馈移位寄存器 (LFSR) 完成。一些移位寄存器串联排列,使用异或/同或门,将后续各级的反馈传回输入。使用的移位寄存器的数量决定了模式的长度或持续时间(图 2)。

图 2:使用异或和同或反馈逻辑实施的四位 LFSR 的示例。反馈抽头确定数据状态的顺序。(图片来源:Digi-Key Electronics)

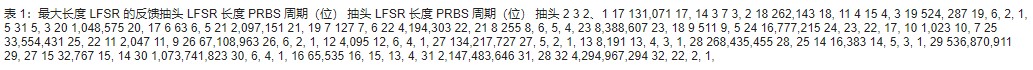

虽然可提供许多种不同反馈配置,但几乎所有设计都使用可产生最大长度序列的抽头,使得状态总数等于 (2N-1),其中 N 是移位寄存器级数。表 1 总结了 LFSR 长度从 2 到 32 的最大长度序列的抽头。这些抽头并不是唯一的。请注意,对于任何给定的移位寄存器长度,可能存在一个以上的最大长度多项式。

表 1:LFSR 长度从 2 到 32 的最大长度序列的抽头汇总。(图片来源:Digi-Key Electronics)

我们的例子使用一个 15 级 LFSR,它产生一个长度为 32,767 位的随机序列,称为 PRBS15 测试序列。通过使用级数更多的 LFSR 可实现更长的序列。使用 PRBS 测试序列的限制在于测试的持续时间。时钟频率为 500 kHz 的 15 位序列需要 65 毫秒 (ms)。31 位序列需要 4295 秒,或大约 72 分钟。

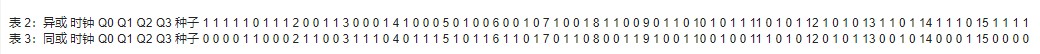

图 2 中的示例使用四个移位寄存器来生成具有 15 种不同状态的数据模式。请注意,两种配置都具有单一禁止状态。对于异或反馈模型,不使用全 0 状态,因为一旦加载,移位寄存器就保持锁定在该状态。同样,在同或实施中,禁止全 1 状态。表 2 和表 3 显示了四位 LFSR 两种配置的数据模式,分别使用三级和四级反馈抽头。

表 2 和 3:或门和或非门配置的数据模式如图 1 所示。(图片来源:Digi-Key Electronics)

两种实施均从已知状态开始,或门下全部为 1,或非门下全部为 0。这些四位最大长度 LFSR 提供 15 种可能的状态 (2N-1),如表中所示。

输出数据模式具有周期性,在 15 个时钟后重复。该模式同时具有确定性,因为对于给定配置和已知的起始状态,可以预测输出。但是,输出模式在 15 个计数周期内是随机的。

设计伪随机二进制序列发生器

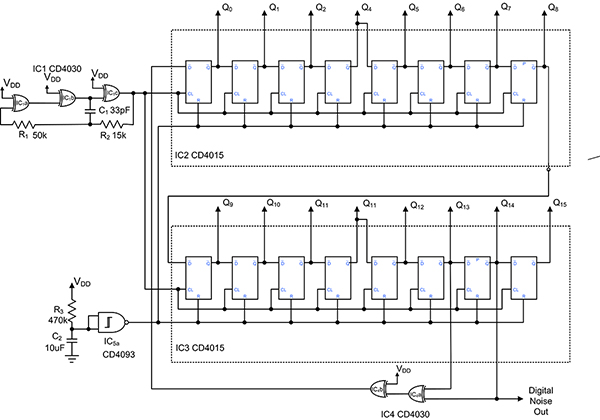

图 3 显示的是一个实用型低成本 PRBS 发生器,其设计基于 LFSR 实施,使用 Texas Instruments 的 CD4015BM96 双四通道静态移位寄存器和 CD4030BM96 四通道异或门。

图 3:使用 Texas Instruments CD4015BM96 双四通道静态移位寄存器和 CD4030BM96 四通道异或门的 PRBS15 发生器的简化原理图。(图片来源:Digi-Key Electronics)

该发生器使用 16 个 D 型触发器(每个 IC 8 个),在第 14 和第 15 级具有反馈抽头,产生 PRBS15 数据模式。反馈连接通过一个异或门进行,然后将其反转以形成一个同或门配置 LFSR。该数据模式长度为 32767 位,在 500 kHz 时钟速率下持续时间约 65 ms。通过使用更长移位寄存器,适当改变反馈抽头,可实现更长的模式。将设计扩展到 31 位模式会将模式持续时间增加到超过 20 亿个状态(在 500 kHz 时钟频率下大约 72 分钟)。

使用 CD4093BM96 施密特触发器与非门 (IC5) 和简单的 RC 网络,发生器在开机时初始化为全零状态。时钟由一个运行在 500 kHz 附近的简单 CMOS 振荡器提供。数字输出可以从任何移位寄存器 Q 输出中获取。在本例下,使用的是 Q14。

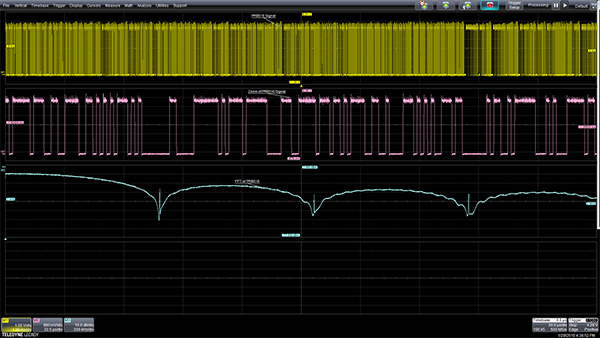

图 4 中的示波器显示了发生器的输出以及输出的快速傅里叶转换 (FFT)。

图 4:发生器的输出(顶部迹线)在中间迹线中水平扩展以便查看详细结构。发生器输出的 FFT(底部迹线)显示,频谱在时钟速率的 1/10 以下平坦。(图片来源:Digi-Key)

数字噪声的 FFT 显示脉冲波形的预期 sin(x)/x 响应,在时钟频率倍数处皆为零。大约 10% 的时钟频率的频谱非常平坦。这是使用低通滤波从数字输出中提取白噪声的关键。

白噪声发生器

白噪声是在其频率范围内频谱平坦的噪声。功率谱密度和每单位带宽的功率在噪声带宽上是恒定的。过滤数字噪声输出后,PRBS 发生器将产生白噪声。

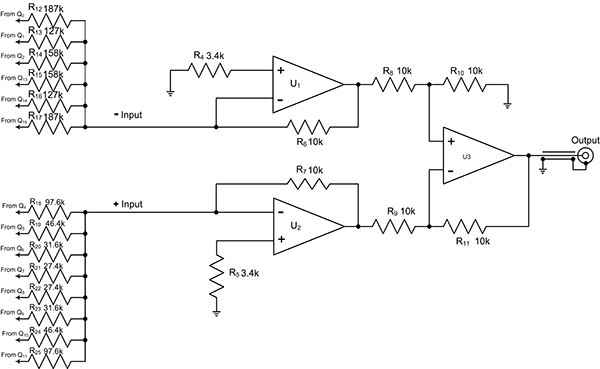

虽然可以使用模拟滤波器,但其将限制在特定时钟频率。通过使用有限脉冲响应 (FIR) 低通数字滤波器,滤波器截止频率将跟踪时钟频率的任何变化。此外,FIR 滤波器可以提供非常低的截止频率,而这对于模拟滤波器而言,需要很大容量的电容器。FIR 滤波器组合了移位寄存器输出的加权和。在频域中产生矩形低通滤波器响应所需的加权是时域中的 sin(x)/x(图 5)。

图 5:发生器的输出级采用来自移位寄存器输出的 sin(x)/x 加权样本,来实现 FIR 低通滤波器。由于 sin(x)/x 加权需要负项,因此使用差分放大器来加总正负加权分量。(图片来源:Digi-Key)

加权移位寄存器输出通过差分放大器求和,差分放大器使用 LM324KDR 四通道运算放大器的三个部分构建。上端电阻器组表示 sin(x)/x 加权的负值。下端电阻器组代表正值。输出 Q3 和 Q12 没有连接,因为它们代表 sin(x)/x 函数的零交叉点。产生的白噪声输出呈现出经典的高斯概率密度函数 (PDF)(图 6)。

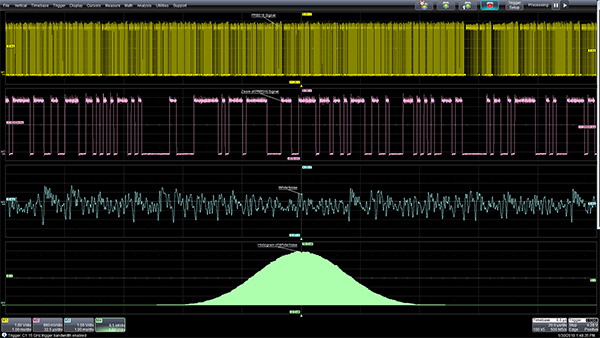

图 6:PRBS 数字噪声(顶部两条迹线)以及模拟白噪声输出(从顶部开始的第三条迹线)。白噪声的直方图(底部迹线)显示了经典的钟形正态或高斯概率密度函数。(图片来源:Digi-Key)

白噪声信号是从顶部向下数的第三条。再往下是噪声的直方图,呈现预期的正态或高斯概率分布。白噪声频宽限制为时钟频率的 5% 或 25 kHz,适用于音频频率测试目的。

总结

如本文所述,可使用现成的 CMOS IC 生成伪随机二进制序列以及模拟白噪声,用于通信和测试应用。所用零件的物料清单花费不多,非常适合学术研究、业余爱好者及有经济意识的工程师和技术人员。

-

CMOS

+关注

关注

58文章

5145浏览量

233274 -

放大器

+关注

关注

142文章

12402浏览量

209900 -

噪声

+关注

关注

13文章

1070浏览量

47059

发布评论请先 登录

相关推荐

如何用LabVIEW生成二进制序列,用于仿真2ASK

用IAR生成原始二进制文件有问题

如何理解二进制运算规则 二进制是如何运算的

如何将Linux源码编译生成二进制

一个源文件生成二进制可执行文件的步骤

什么是二进制计数器,二进制计数器原理是什么?

二进制电平,什么是二进制电平

prbs伪随机码介绍

如何使用PRBS和CMOS器件生成伪随机噪声和二进制序列

如何使用PRBS和CMOS器件生成伪随机噪声和二进制序列

评论