最近是跟内存耗上了,其一是手里没有其它硬件可测,更重要的是想趁着这段时间,把内存与性能之间的影响都慢慢测一下。今天测的就是时序与内存性能之间的关系了。时序很重要吗?答案是肯定的,但是时序对内存性能的影响到底有多大呢?下面就详细的测试一下。

用来测试的内存,是宇瞻突击队Commando DDR4 2400内存(4GX4)套装。这是一套很特别的产品,4GX4的组合还是比较少见的,现在多数都是8GX2的组合。

内存的规格为4GB UNB PC4-19200 CL 16-16-16-36,其中PC4代表台式机DDR4。19200是用带宽来命名,2400*64/8=19200(内存带宽的计算公式:带宽=频率*位宽/8),2400是DDR等效频率,16-16-16-36是内存的时序。

一:时序15-15-15-36

使用OC项中的Memory Try It !选项,选择DDR4-3200MHz CL15频率,CL15就是指内存的时序。

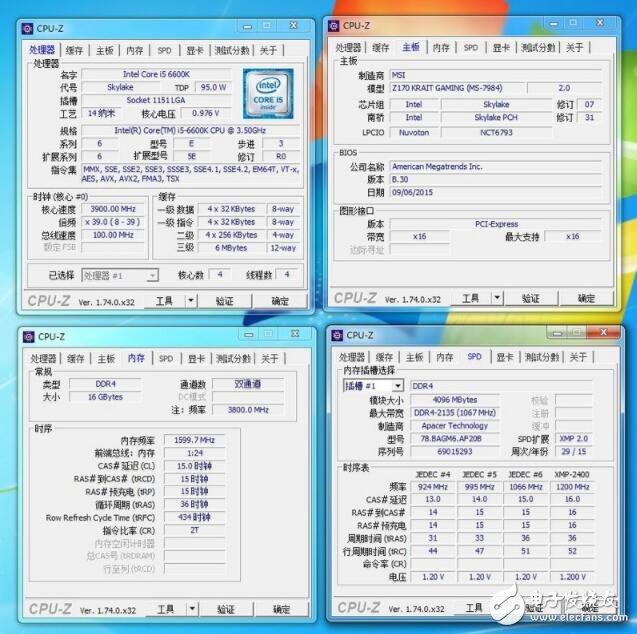

DDR4-3200MHz CL15频率下的时序信息。

进入系统后,打开CPU-Z软件,可以看到内存已经在3200MHz的频率下运行了。这个频率下宇瞻突击队4GB DDR4 2400内存套装的时序为15-15-15-36,内存的TRFC为434时钟,CR为2T。

为了使测试的数据更加准确,这里选择使用AIDA64软件进行测试,这软件的更新的频率非常的高,基本上十天,半个月就一次。

在Memory Benchmark测试中,Read、Write、Copy的速度(单位MB/S)分别是42663、47405、42840。

二:时序16-16-16-36

使用OC项中的Memory Try It !选项,选择DDR4-3200MHz CL16频率。

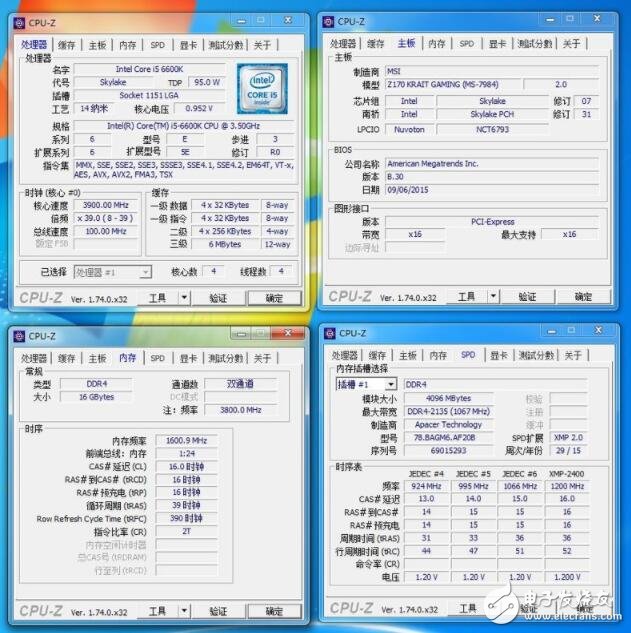

DDR4-3200MHz CL16频率下的时序信息。

打开CPU-Z软件,可以看到内存依旧是在3200MHz的频率下运行,不过它的时序已经发生了变化。这时宇瞻突击队4GB DDR4 2400内存套装的时序为16-16-16-36,内存的TRFC为390时钟,CR为2T。

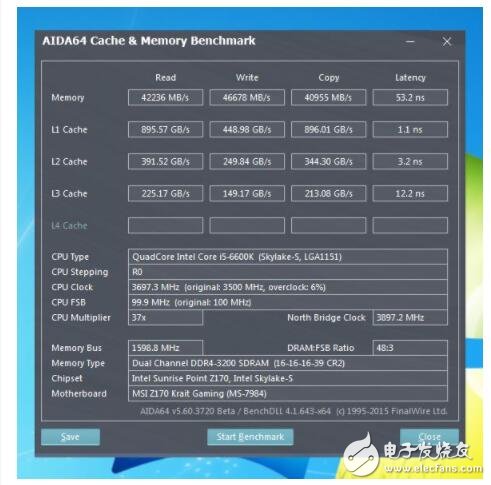

在Memory Benchmark测试中,Read、Write、Copy的速度(单位MB/S)分别是42236、46678、40955。可以明显的看到内存的性能已降低了。

三:时序18-18-18-39

使用OC项中的Memory Try It !选项,选择DDR4-3200MHz CL18频率。

DDR4-3200MHz CL18频率下的时序信息。(在这个时序下,超频失败,无法进入操作系统。)

小结:测试的结果已经很明确了,同频率下内存的时序越低,得分就越高。如果时序过高的话,会造成内存超频失败。所以在超频时一定要重视内存的时序,避免出现高频低能,空有频率,性能却一塌糊涂的现象。

-

内存

+关注

关注

8文章

2760浏览量

72698 -

时序

+关注

关注

5文章

356浏览量

36952

发布评论请先 登录

相关推荐

lpddr5时序比ddr5慢多少

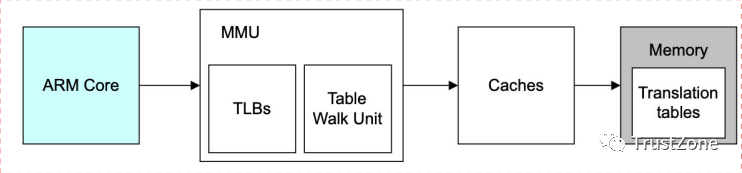

内存管理单元的重要功能是什么

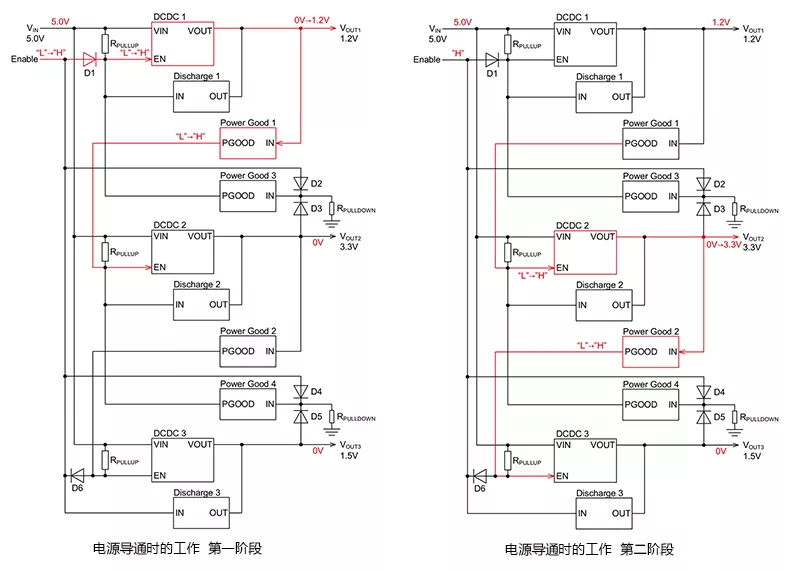

soc中的组合逻辑和时序逻辑应用说明

路由器内存和cpu哪个重要

什么是时序?由I2C学通信时序

兼顾内存和速度的C语言代码优化的方法

静态时序分析的基本概念和方法

同步电路设计中静态时序分析的时序约束和时序路径

FPGA速度-面积互换原则设计

内存速度和时序重要么

内存速度和时序重要么

评论