今天我们来介绍一下如何修复ECO阶段的Noise Violation. 首先,我们也来介绍一下什么是Noise。

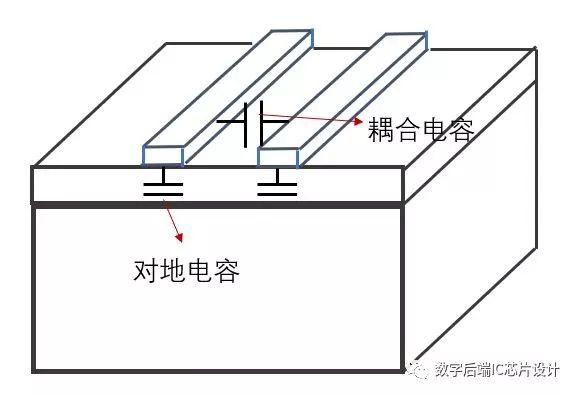

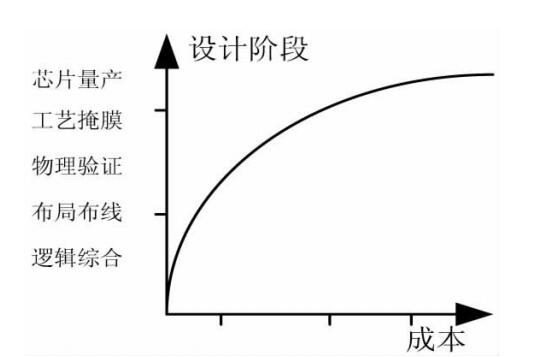

网上资料很多,大致整理一下,noise(噪声)也称为crosstalk(串扰),signal integrity(信号完整性分析),是随着芯片特征尺寸变小后引发的现象。主要指工艺金属层线变窄,间距变小以后,导致线与线之间的耦合电容(coupling capacitance)增大,接地电容变小(如下图所示)。而Noise的大小与耦合电容成正比,与接地电容成反比。所以导致Noise的影响变大。

那么在后端PR中,noise对我们的影响,主要分为两大类:信号的延迟(delay)和毛刺(glitch)。这两类问题都会对芯片的性能产生影响。

Noise与信号延迟

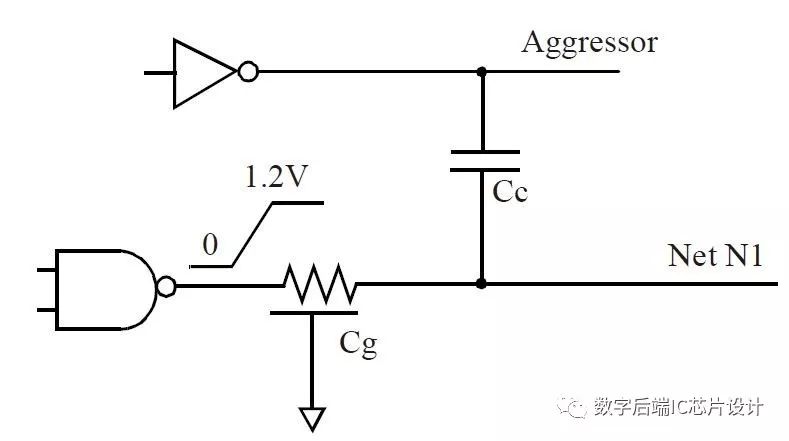

首先我们来讲下noise对信号延迟的影响,在分析noise时,我们将产生noise信号源的网络称为侵害网络(aggressor net或attacker),受到串扰的网络称为受害网络(victim net)。当aggressor的信号在0 和1之间电平变换时,victim上会产生相应的串扰噪声,这种转换噪声能使victim的信号转换变慢或变快。如果victim受到相同方向跳变的aggressor,会造成它的delay变小;如果victim受到相反方向跳变的aggressor,会造成它的delay变大。

如下图所示:Net N1作为victim,与Aggressor有Cc的耦合电容。假设Net N1正在0~1发生跳变。如果aggressor也在发生0~1的跳变,那么它的上升沿会耦合到N1上面,会造成N1的delay变小;如果aggressor正在发生1~0的跳变,那么它的下降沿作用到N1上时,该信号转换变慢,会造成它的delay变大。

Noise虽然会对信号延迟产生影响,恶化时序。但是,如果在它影响下,时序依然可以signoff,那么我们可以不必去修复它。

Noise与毛刺

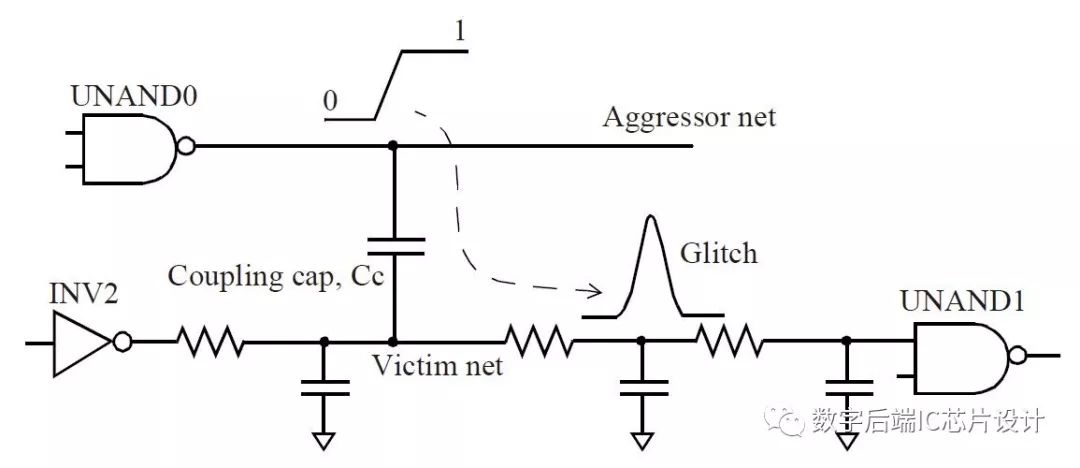

Noise引发的另一种现象,我们称为毛刺(Glitch)。如下图所示,当victim net受到aggressor net跳变影响时,就会有毛刺信号通过耦合电容引入。

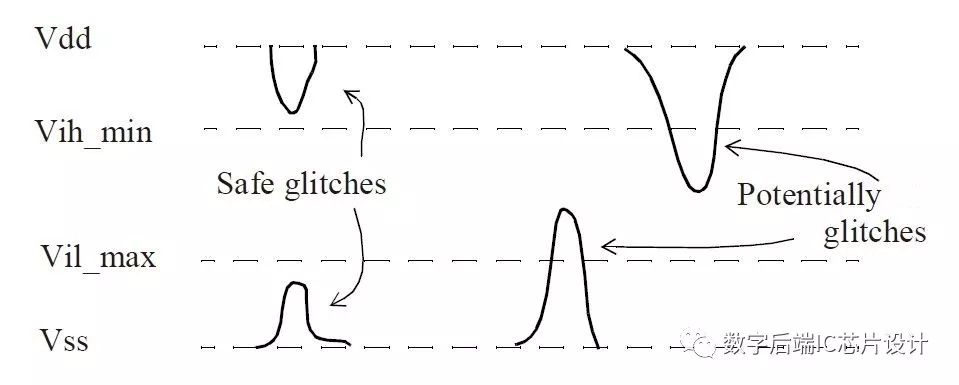

如下图所示,有时候,这个毛刺信号比较小,可以忽略;但是,当毛刺信号足够高而且持续时间较长,这就有可能导致逻辑功能发生变化,破坏了门电路所保存的状态,使得电路发生故障。因此,在最后timing signoff中,noise引起的glitch是我们必须要修复的violation。

那么,在后端PR中,如何来修复Glitch呢?

有很多方法,下面列举几种;

(1)降低aggressor net的驱动能力

aggressor net的驱动能力越强,Glitch的量级就越大。

(2)增强victim net的驱动能力

victim net驱动能力越弱的话,Glitch的量级也会越大。使用髙驱动单元可提髙潜在victim net的门限,从而降低victim net的受害程度。

(3)保护victim net

将victim net和aggressor net之间的间距加大,或者采用屏蔽线shielding都是保护victim net的一些好方法。

(4)给victim net插入Buffer

插buffer是后端修复violation的万能手段。它也是是处理noise时一项非常有效的修复技术。通过插入buffer将长线打断能有效降低victim net上的耦合电容,从而降低noise的影响。

-

信号完整性

+关注

关注

65文章

1334浏览量

94906 -

Noise

+关注

关注

0文章

19浏览量

11143

原文标题:愁绪千万端,扰乱不成眠——如何修复Noise?

文章出处:【微信号:IC_Physical_Design,微信公众号:数字后端IC芯片设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ECO TO PCB问题

FPGA编译在place步骤显示“unusual high hold time violation detected”

如何解决“access violation at address”错误

汽车eco模式使用技巧_eco模式真能省油吗

eco模式的好处以及坏处_eco模式会引起积碳是真的吗

我们如何来修复setup violation?

如何来手动修复max transition和max capacitance

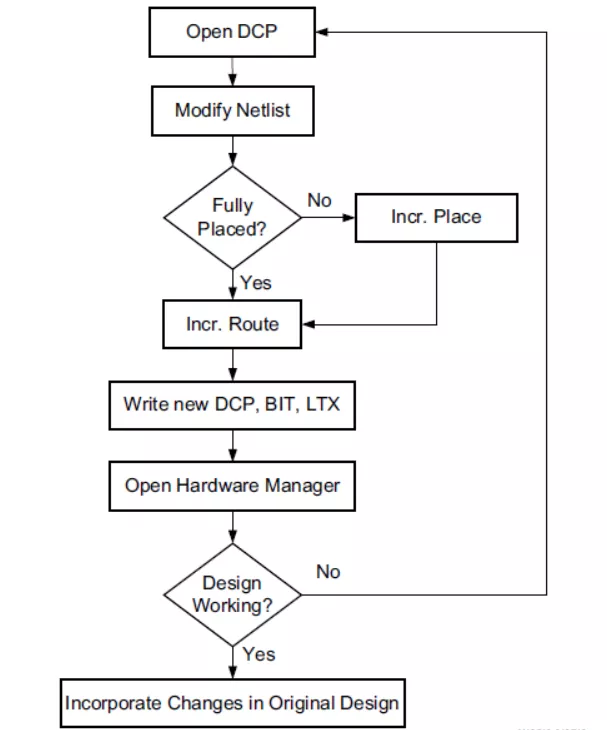

如何在Vivado中执行工程变更命令 (ECO)

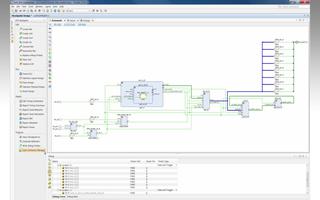

图形界面介绍:GUI上的按键是Violation Browser

ECO技术在SoC芯片设计中的应用

空调遥控器上的eco是什么意思

详解Xilinx FPGA的ECO功能

如何修复ECO阶段的Noise Violation

如何修复ECO阶段的Noise Violation

评论