UART(串口)收发模块设计- 01

UART协议介绍

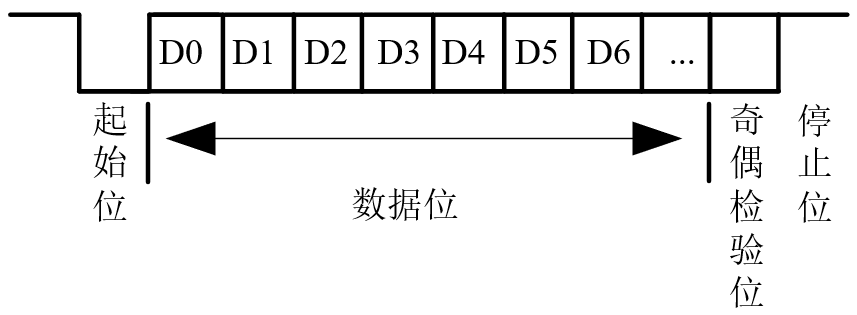

UART作为异步串口通信协议的一种,工作原理是将要传输的数据一位一位地传输。其中每一位(bit)的意义如下。

空闲位:在无数据传输的时候,传输线上的电平为高电平,即为空闲位。

起始位:当开始传输数据时,先发出1bit位宽的低电平,表示数据开始传输,即为起始位。

数据位:真正的需要发送的数据,位宽可以为4到10bit。数据从低bit开始向外一位一位的发送。

奇偶校验位(可不要):当数据发送完毕后,再发送1位校验位,以此来校验数据传送的正确性。

(偶校验:数据位加上这一位后,使得“1”的位数应为偶数

奇校验:数据位加上这一位后,使得“1”的位数应为奇数)

停止位:在最后发送一位高电平的停止位。

UART每一位的位宽时长由波特率决定,波特率既1s发送的数据位数。一般选择的波特率有,9600,19200,115200等。

设计实例概述

本设计代码链接:https://pan.baidu.com/s/1VJoSPJRSHYMhmx3rs2t4IA

提取码:jsak

复制这段内容后打开百度网盘手机App,操作更方便哦

本实例设计的UART特性:

(1) 并没有支持奇偶检验,故没有奇偶校验位

(2) 并不支持数据位宽可配,数据位位宽固定为8bit。

(3) 支持输入时钟与波特率可配。

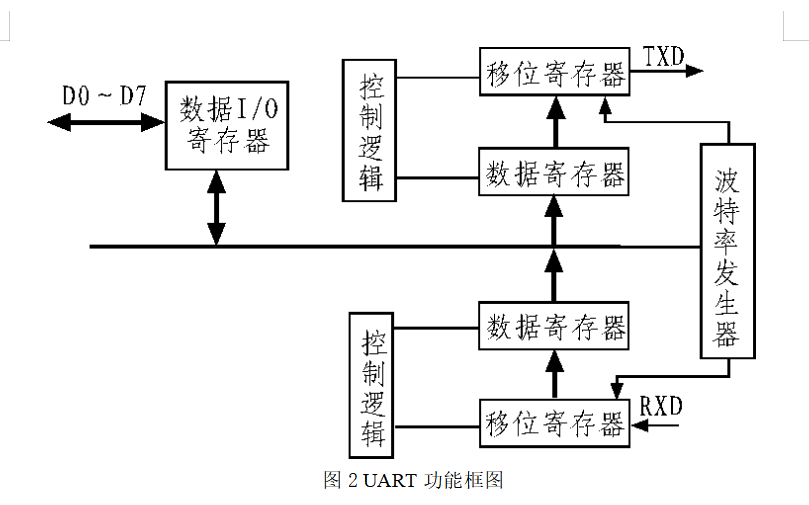

原理图如下,分两个大模块,一个数据接收控制模块(Receive_Control),一个数据发送控制模块(Send_Control):

端口说明:

接收控制模块与发送控制模块内部都有一个波特率时钟产生模块(BuadRate_set),用于将电路输入时钟(clk)进行分频产生波特率时钟,用于接收和发送数据控制。

可以看到,BuadRate_set模块有一个enable控制信号,只有当enable信号为高时,BuadRate_set模块才工作。在发送控制模块里面,只有发送数据的时候才拉高其相应的enable;在接收控制模块里面,只有检测到有数据发送进来的时候才拉高其相应的enable。这是为了降低功耗。

后文预告

后文将会具体介绍内部各个模块的设计细节以及收发速度匹配和仿真验证等问题。

-

控制模块

+关注

关注

2文章

118浏览量

18630 -

uart

+关注

关注

22文章

1156浏览量

99942 -

异步串口

+关注

关注

0文章

9浏览量

9175

原文标题:UART(串口)收发模块设计- 01

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

协议栈介绍--TCP/IP

协议栈介绍

用verilog实现UART协议理解何为接口以及如何进行模块化设计

FPGA片内FIFO的功能概述和模块划分

请问我怎样设置实现串口UART通信?

UART串口通讯协议是什么

了解一下DMX512的基本协议

DMX512的基本协议相关资料分享

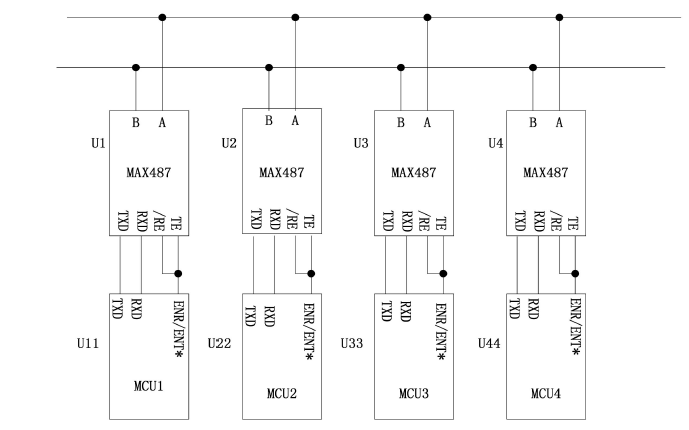

如何设计和实现基于UART的机器人分布式控制通信协议概述

使用FPGA和模块化设计方法实现UART的设计论文

振弦采集模块UART 通讯协议

UART的基本协议与设计实例模块划分以及整体实现概述

UART的基本协议与设计实例模块划分以及整体实现概述

评论