过去的一年,我们在处理器市场看到了AMD的崛起和Intel的颓势。Intel的7nm工艺迟迟没有进展,而AMD却抢先发布了第一款基于7nm的处理器。当然,Intel也不会坐以待毙,最近发布了基于3D堆叠芯片的新架构Foveros,在采访中更是坦言摩尔定律还有很多空间值得挖掘。本文将分析3D堆叠架构对于Intel以及未来处理器市场的重要影响。

More Moore与More than Moore

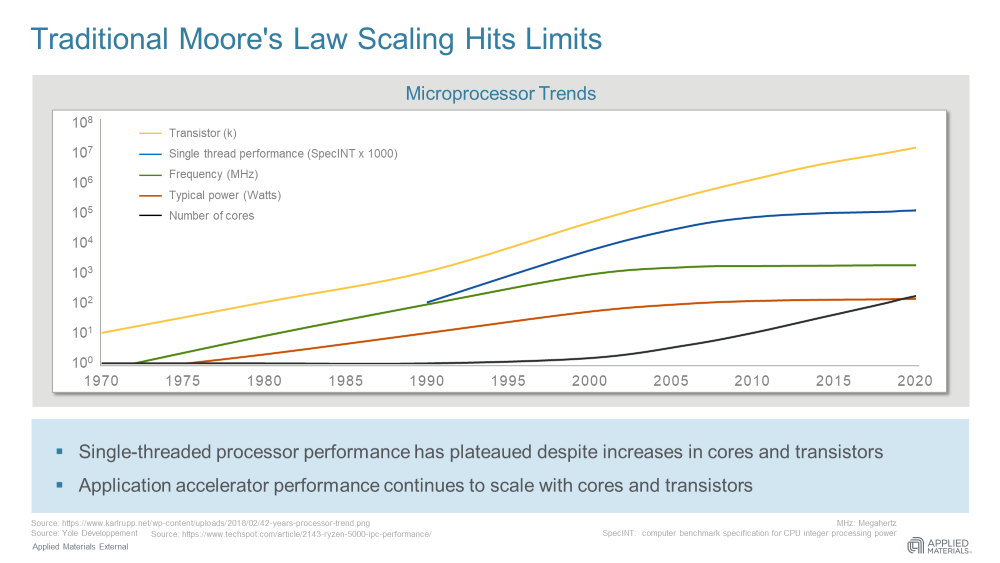

随着摩尔定律经过数十载的发展,目前片上晶体管的尺寸已经离技术极限不远。这意味着按照摩尔定律进一步缩减晶体管特征尺寸的难度越来越大。于是,半导体工艺下一步发展走到了十字路口。

在过去摩尔定律的黄金时期,其背后的逻辑是:半导体行业需要以一个合适的速度增长以实现利润的最大化。随着制程的进化,同样的芯片的制造成本会更低,因为单位面积晶体管数量提升导致相同的芯片所需要的面积缩小。所以制程发展速度如果过慢,则意味着芯片制作成本居高不下,导致利润无法扩大。因此,摩尔定律背后的终极推动力其实是经济因素。同时,随着半导体特征尺寸下降,芯片的性能也会上升,因此缩小晶体管的特征尺寸可谓是一举两得。

然而,随着半导体工艺接近极限,进一步做小特征尺寸越来越贵,在16nm节点时半导体厂商纷纷引入了FinFET和multi-pattern技术,在减小特征尺寸的同时却也大大增加了半导体工艺的成本;到了7nm又要开始引入EUV,甚至到了5nm以下的节点FinFET也不够用了有可能需要使用更新一代的Gate-all-around器件,这又回进一步提升成本。因此,现在的新半导体工艺仅仅是在出货量足够大的时候才能赚回高昂的成本,这也是现在只有少部分公司有能力和决心使用最新半导体工艺的原因。换句话说,特征尺寸继续缩小的经济推动力在目前7nm的节点已经较小。

另一方面,甚至性能上的推动力也不如以往。之前晶体管特征尺寸每缩小一次,性能都会有接近50%的提升,而现在特征尺寸在7nm附近每次缩小带来的性能提升已经所剩无几,其主要改善主要来自于能效比的提升(每次晶体管特征尺寸缩小仍然能带来40%左右的显著能效比提升)。

在这样的情况下,是否要进一步通过缩小晶体管特征尺寸来继续半导体行业的发展成为了一个问题。一个方向当然是延续摩尔定律的路子继续缩小特征尺寸(即More Moore),引入新的光刻技术,引入新的器件等等,例如三星就发布了用于3nm的Gate All-Around FET路线图,然而随着性能和经济学推动力变弱,这样的路径还能走多远不好说。另一个方向就是用其他的路径来代替摩尔定律通过缩小晶体管特征尺寸实现的经济学和性能推动力,来延续半导体行业的发展。这样的路线就是More than Moore路线。

More than Moore目前的一种主流模式是通过高级封装技术来实现。首先改变之前SoC单芯片越做越大越做越复杂的传统思维,在More than Moore中把芯片划分成多个不同的模块,每个模块分别用合适的半导体工艺实现(成为芯片粒chiplet),最后不同的chiplet再用高级封装技术集成在同一个封装内。Marvell提出的Mochi架构就是典型的More than Moore思路,使用不同半导体工艺的芯片粒分别实现CPU、GPU、Modem、WiFi等不同模组,不同芯片粒之间使用标准的高速接口进行通信,并封装在同一封装内。

在More than Moore中,经济学的推动要素来自于使用最适合的工艺来实现不同的模块。例如,使用成熟的28nm甚至65nm来实现模拟电路,而使用最新的7nm来实现高性能数字逻辑,其成本比起全部使用最新半导体工艺来实现所有模块要便宜得多。而在性能方面,More than Moore的推动力则来自于新的体系架构,例如在高级封装中可以为处理器和存储器之间提供远高于传统方案的内存带宽(HBM和HBM2),内存带宽的提升一方面改善了系统性能,另一方面也为新的计算机体系架构设计打开了大门。总而言之,在More Moore方向中,晶体管缩小同时是成本降低和性能提高的驱动力;在More than Moore方案中,成本降低来自于芯片中不同模块各自使用最合适的工艺,而性能提升则来自于新的电路设计。

More than Moore的高级封装技术传统方案主要有2.5D和3D两种。2.5D技术是指将多块芯片粒在硅载片(silicon interposer)上使用互联线连接在一起,由于硅载片上的互联线密度可以远高于传统PCB上的互联线密度,因此可以实现高性能互联。其典型的技术即TSMC推出的CoWoS,InFO以及Intel的EMIB等技术。而传统的3DIC技术则是将多块芯片堆叠在一起,并使用TSV技术将不同的芯片做互联。目前,3DIC主要用在内存芯片之间的堆叠架构和传感器的堆叠,而2.5D技术则已经广泛应用在多款高端芯片组中。另外3D和2.5D之间也不是完全对立,例如在HBM内存中,多块内存之间使用3DIC集成,而内存与主芯片之间则使用2.5D技术集成在一起。

Intel的3D堆叠技术:

More than Moore的新发展

Intel在高级封装领域一直处于领先地位,之前的EMIB技术就有其独到的优势,而这次Intel发布的Foveros架构则是3DIC方面一个长足的进步。

Foveros架构中,芯片3D堆叠在硅载片上,并通过硅载片做互联。Foveros进步在于其硅载片从原来的无源硅载片变成了有源硅载片。在之前的典型2.5D封装中,硅载片上只是做互联线供芯片之间做互联,因此是无源硅载片。而在Foveros架构中,硅载片是有源的,即硅载片上除了互联线(无源)之外,还包含了有源电路 。如果说传统的2.5D封装中的硅载片只是一种载片,那么载Foveros中的有源硅载片实际上就是一块真正的芯片了,而这次的计算和存储芯片是堆叠在一块真正的芯片上,因此可以说是名副其实的3DIC。相比2.5D封装,使用Foveros的3D封装大大提升了集成密度,同时芯片与有源硅载片之间的IO带宽也有潜力能做更大,从而获得更大的性能提升。

在2019年即将发布的Foveros芯片组中,Intel计划将一块使用10nm工艺的高性能计算芯片粒(P1274)堆叠在一块使用22nm工艺的有源硅载片SoC(P1222)上。22nm的硅载片上具体拥有哪些模块还不清楚,但是预计主要的IO接口(如DDR)电路将会在这块有源硅载片上实现,因为IO电路并不需要10nm这样的尖端工艺,使用22nm无论是对于成本、良率还是混合电路设计难度来说都是最适合的。事实上,这也符合了More than Moore的精神,即使用最合适的半导体工艺去实现相应的模块,从而实现成本的降低,成为半导体行业继续演化的经济学动力。Intel在发布会上暗示,未来可能会把混合信号电路和存储器做在这块有源硅载片上,这也为3DIC有源硅载片技术带来了很大的想象空间。

事实上,Intel在12月发布的Foveros多少也是对AMD于11月发布的Rome架构处理器的回应。11月,AMD发布的Rome架构处理器也是基于高级封装,由多块7nm Zen2处理器芯片粒和一块14nm 互联和IO芯片使用2.5D技术封装而成,其中每块7nm Zen2芯片粒都含有8个核,而多块芯片粒经过组合最多可以实现64核,芯片粒之间则通过14nm互联芯片进行芯片间通信。AMD Rome和Intel Foveros使用芯片粒加高级封装的基本思路如出一辙,但是Intel Foveros使用了3D封装而AMD Rome使用的是2.5D,因此在封装技术上Intel更胜一步,至于Intel 3D封装带来的性能提升是否能抵消AMD使用7nm领先半导体工艺的优势,我们不妨拭目以待。从另一个角度来看,事实上使用More than Moore高级封装技术已经成为了半导体行业旗舰公司的共识,未来可望从高端处理器芯片慢慢普及到更多芯片品类。

More than Moore能走多远

Intel的Foveros是More than Moore高级封装技术的最新发展,其使用的3D堆叠技术相较于之前的2.5D技术可谓是一大进步。然而,在把2.5D变为3D之后,More than Moore接下来的路又该怎么走?在之前的摩尔定律时代,只要缩小特征尺寸即可;而在More than Moore时代,又该如何继续挖掘潜力以延续摩尔定律的辉煌呢?

我们认为, 现在半导体行业采用More than Moore的主要目的首先是为了提升性能,而非提高集成度以降低成本。芯片行业经过了数十年的发展,已经早已成为了大量新技术的基石:移动通信、多媒体、人工智能、区块链等等对于社会拥有强大驱动力的技术无一不以高性能芯片为基础。这些新技术应用对于芯片性能提升的需求远远大于芯片成本降低的需求。这也是为什么去年AMD抢先使用7nm对Intel造成巨大影响的原因,因为7nm新工艺意味着更强大的性能(而非更低的成本)。事实上,这次Intel推出的Foveros的部分原因也是希望其高性能10nm处理器能尽快量产,而仅仅把核心逻辑电路部分用10nm工艺实现而其他部分用成熟的22nm工艺做显然能改善整体芯片组的良率,从而让高性能芯片组早日进入商用。总之,将来半导体先进工艺的进化动力将主要来自于性能提升而非成本降低。

那么,More than Moore对于性能的提升主要来自于哪里呢?除了之前说的可以降低使用最先进半导体工艺芯片粒的面积以提升良率,从而加快新工艺芯片上市速度间接提升性能之外,更主要的性能提升空间来自于封装技术本身的性能提升以及芯片新架构带来的性能提升。

从高级封装技术本身来说,其主要的性能提升主要是指更高密度、支持更高频率信号的互联线,以及更复杂的堆叠模式。互联线方面的提升带来的最直观性能改善来自于更高芯片之间(包括处理器与内存)的通信带宽。在高级封装出现之前,芯片间通信的带宽往往取决于PCB板上走线的密度以及其走线支持的信号频率,而PCB板这里是摩尔定律管不到的地方。2000年第一代DDR推出时的接口频率是100MHz,而到2015年未使用高级封装的DDR4 的接口频率是1200MHz,内存带宽在15年间仅上升12倍,这远远小于处理器的性能提升速度,因此内存带宽事实上成为了系统性能的瓶颈,即所谓的“内存墙”。而当基于高级封装的HBM出现时,一下将内存带宽由DDR4时代的19.2GB/s提升到了128GB/s,HBM2更是提升到了256GB/s,可谓是质的提升。HBM带来的性能提升主要来自于高级封装优质的互联线,一方面走线密度大大提升,之前DDR系列的借口宽度为64,而HBM则提升到了1024;

另一方面由于高级封装走线对于高频信号的支持远好于传统PCB,因此未来有更大的潜力能继续提升芯片间的通信速度,从而让“内存墙”问题不复存在。在堆叠模式方面,我们看到了Foveros从2.5D进化到了3D,未来可望还能实现更多层次的堆叠等。然而,新的堆叠工艺开发难度远高于高级封装内走线密度的提升,因此我们在未来几年内更有希望看到的是使用高级封装技术带来的更方便灵活同时也速度更高的芯片间通信。

除了高级封装本身带来的直接性能提升,More than Moore在未来对于芯片的性能提升潜力来自于新的处理器架构设计。事实上,学术界和业界在新的处理器架构上的研究已经有非常多的积累,但是由于标准CMOS工艺的各种考量一直没有商业化,而随着More than Moore高级封装技术的到来,这些研究都可望能实用化,从而成为半导体行业的重要驱动力。例如,众核架构之前已经研究了很久,但是以往的技术在实施众核架构时会遇到各种实际的问题。如果把众核集成在一块芯片上,则芯片面积可能过大而导致良率问题;如果把众核封装成不同的芯片,则芯片间通信的开销会过大。现在随着高级封装技术的来临,可以把众核做成多个芯片粒,并用硅载片上的高速总线进行芯片间通信,从而充分发挥众核架构的设计优势。

事实上,我们看到AMD Rome使用多个芯片粒组合成64核处理器正是一个印证。除了众核芯片之外,各种新存储器也将从More than Moore路线中获益。新存储器,如MRAM,ReRAM等,能提供很高的存储密度和很低的访问延迟,但是因为需要特殊工艺因此很难直接集成到使用最新半导体工艺的SoC上,这也是之前新存储器商用化较慢的一个原因。现在有了高级封装则无需再担心工艺的兼容性问题,而是完全可以把SoC和存储器做成不同的芯片粒,然后用硅载片连接到一起。这样同一封装内的新存储器可以作为新的大容量缓存单元,从而提升处理器的性能。最后,More than Moore和目前流行的异构计算相结合也能获得良好的效果:异构计算主张把不同的计算使用专用化的计算处理单元来完成以实现高性能高效率计算,而More than Moore路线则可以把异构计算中使用到的专用计算处理单元用合适工艺的芯片粒实现,然后用高级封装技术实现互联和封装。这样通过类似乐高积木一样组合不同的专用化处理模组芯片粒,就可以快速而高效地设计出高性能专用芯片模组。

综上,结合高级封装技术本身的技术提升,More than Moore路线开启的新架构设计以及异构计算的新设计理念和设计生态,我们预计在未来处理器至少还能实现10倍以上性能提升。而且,在More than Moore时代,芯片性能提升中,设计师的重要性大大提升,因此未来将是芯片设计的好时代。

-

摩尔定律

+关注

关注

4文章

622浏览量

78517 -

intel

+关注

关注

19文章

3451浏览量

184768

原文标题:Intel的3D堆叠能否为摩尔定律续命?

文章出处:【微信号:WW_CGQJS,微信公众号:传感器技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

摩尔定律的终结:芯片产业的下一个胜者法则是什么?

英特尔CEO基辛格:摩尔定律放缓,仍能制造万亿晶体

后摩尔定律时代,Chiplet落地进展和重点企业布局

什么是摩尔定律,“摩尔定律2.0”从2D微型化到3D堆叠

摩尔定律不会死去!这项技术将成为摩尔定律的拐点

超越摩尔定律,下一代芯片如何创新?

半导体行业产生深远影响的定律:摩尔定律!

什么是摩尔定律?

Intel用3D堆叠技术为摩尔定律续命

Intel用3D堆叠技术为摩尔定律续命

评论