该组项目将使研究机构和公司能够使用Achronix高性能Speedcore eFPGA技术快速构建低成本测试芯片

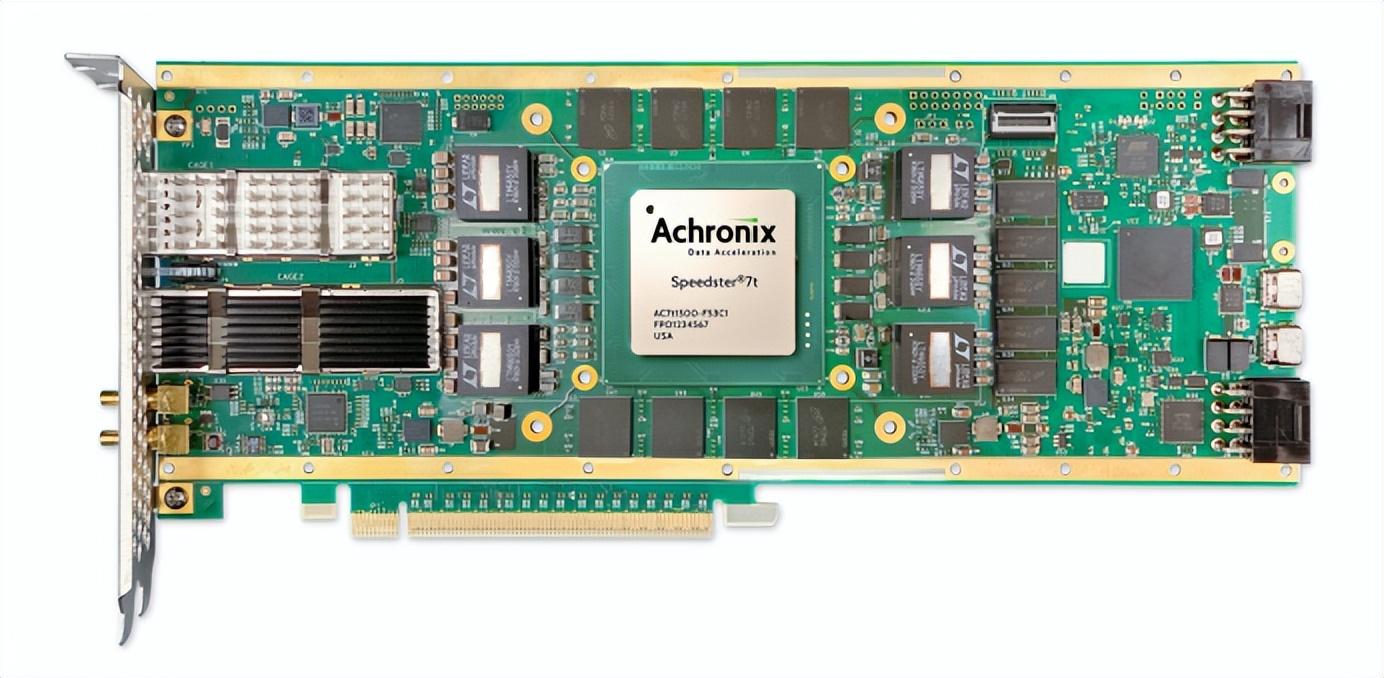

基于现场可编程门阵列(FPGA)的硬件加速器器件和高性能嵌入式FPGA半导体知识产权(eFPGA IP)领导性企业Achronix半导体公司日前宣布:公司推出两个全新的项目,以支持研究机构、联盟和公司能够全面对接Achronix领先Speedcore eFPGA技术。

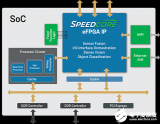

eFPGA技术正在迅速地成为基于系统级芯片(SoC)的CPU卸载功能中可编程硬件加速单元的必备硅知识产权(IP),已被广泛用于包括人工智能/机器学习(AI / ML)、区块链、网络加速、智能网卡和智能物联网等各种应用。这些被称为“eFPGA Accelerator”的eFPGA应用加速项目面向希望试验或证实新硬件架构的研究机构和测试芯片开发人员,为其提供了获得公司Speedcore eFPGA IP预先配置版本及相关开发工具的对接机会。

研究类eFPGA Accelerator应用加速项目:

大学、政府机构和行业联盟经常工作在技术进步的前沿, Achronix承诺支持这些类型的前沿研究项目。 Achronix的全新研究类eFPGA Accelerator应用加速项目将支持研究人员使用预先配置的Speedcore eFPGA IP,在他们的SoC研究项目中构建可编程硬件加速器。这类项目还针对政府机构的高性能计算需求,解决这些需求中确实需要解决的关键安全性和硬件保障问题,尽管他们通常缺乏去摊销开发定制SoC费用的制造批量。

测试芯片类eFPGA Accelerator应用加速项目:

测试芯片类eFPGA Accelerator应用加速项目使各种公司能够将eFPGA IP集成到其ASIC和SoC之中,从而利用Achronix经过流片验证的、预先配置好的IP及支持性ACE设计工具。跨越许多个应用领域和地区的公司都希望测试其包含可编程硬件加速器的新体系结构设计,从而满足计算、联网和存储平台的高性能应用需求。测试芯片类eFPGA Accelerator应用加速项目支持这些公司便捷地将经过流片验证的高性能eFPGA IP集成到其ASIC和SoC的设计中,然后根据评估批量来制造芯片。

“Achronix很高兴能够走在嵌入式FPGA市场的最前沿,该技术正在迅速地成为许多需要硬件加速的应用的首要选择”,Achronix市场营销副总裁Steve Mensor说道。“这些全新的eFPGA Accelerator应用加速项目将使创新的公司和研究机构能够使用我们的IP和工具去构建下一代的可编程芯片,从而满足AI / ML和其他计算密集型应用不断增长的数据和计算量需求。”

Achronix 的研究类eFPGA Accelerator应用加速项目和测试芯片类eFPGA Accelerator应用加速项目,将支持研究机构和测试芯片开发人员轻松地获得Achronix的Speedcore eFPGA技术的许可授权。该项许可包括对接预先配置的、经过流片验证的Speedcore eFPGA IP以及该公司业内一流的ACE设计工具。所有标准的Speedcore交付物都将包含在这些应用加速项目中。这些项目的Speedcore IP都是基于台积电(TSMC)的16FF +工艺技术。

-

FPGA

+关注

关注

1602文章

21305浏览量

593112 -

AI

+关注

关注

87文章

26413浏览量

264021 -

区块链

+关注

关注

110文章

15554浏览量

104757

原文标题:Achronix半导体全面对接Speedcore eFPGA技术

文章出处:【微信号:FPGAer_Club,微信公众号:FPGAer俱乐部】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

中高端FPGA如何选择

Achronix FPGA增加对Bluespec提供的基于Linux的RISC-V软处理器的支持,以实现可扩展数据处理

Achronix与Bluespec联合宣布推出一款支持Linux的RISC-V软处理器

半导体发展的四个时代

半导体发展的四个时代

Achronix以创新FPGA技术推动智能汽车与先进出行创新

半导体≠芯片:你真的了解半导体技术吗?

请问AD7626与FPGA如何对接?

国产FPGA简介

基于Speedcore eFPGA IP构建Chiplet

Achronix“内外兼修”赋能AI/ML数据加速

广东省汽车半导体和元器件应用产业联盟供需对接活动“走进深圳“成功在国民技术举办

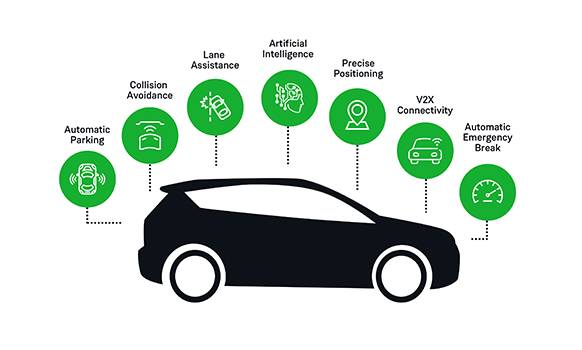

为什么嵌入式FPGA(eFPGA)IP是ADAS应用的理想选择?

Achronix半导体全面对接Speedcore eFPGA技术

Achronix半导体全面对接Speedcore eFPGA技术

评论