作为浸润式光刻方法的开创者,中国***新竹清华大学、新竹交通大学、***大学特聘讲座教授,以及清大-台积电联合研发中心主任,2018年未来科学大奖-数学与计算机科学奖获奖者,林本坚博士于近日作客北京清华大学,向师生及业界人士详解了半导体光刻技术及其发展历程,展示了一个详尽、立体的光刻世界。

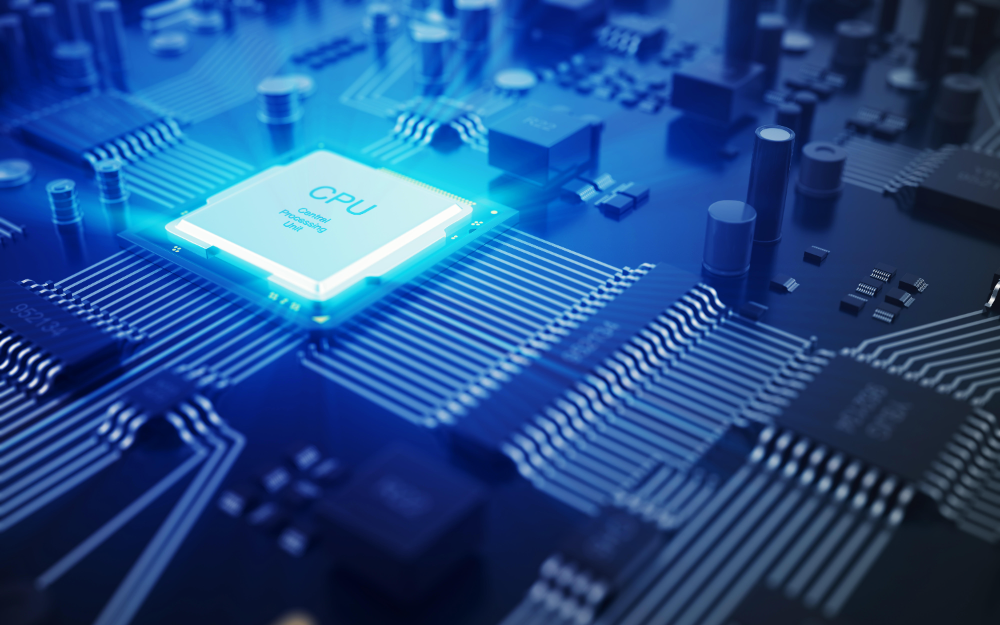

当人类刚发明出集成电路的时候,当时的特征尺寸大概是5μm(5000nm),之后缩小到了3μm,发展至今,台积电已经开始量产7nm的IC了。在这个过程当中,制程共经历了20代变革,未来几年,5nm集成电路也将实现量产。从5μm到5nm,实现了1000倍的变化,大概经历了40年。

在这一过程当中,有一件比较神奇的事情,5μm阶段,当时的波长是436nm,而到当今的7nm,波长是193nm,变化并不是特别大,这样,从光学的角度看,我们要实现将特征尺寸缩到波长的四十分之一,似乎是不可能完成的任务,我们需要跳出纯光学思维,从半导体的角度去考虑如何实现它。

人的头发横截面直径大概是80μm,以采用28nm制程工艺的SRAM为例,可以在头发的横截面上放20735个这个样的SRAM单元,随着微缩技术的发展,在直径为80μm的横截面上,可以容纳越来越多的SRAM单元了。

那么,这是如何做到的呢?主要是由光刻工艺及其技术演进实现的。

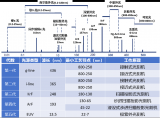

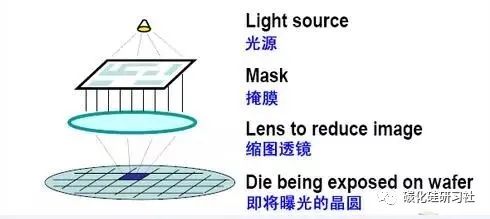

光刻微缩的理论基础主要基于下图的方程式:分辨率和DOF(depth of focus,景深)。

从图中的公式可以看出,分辨率主要由三个因数决定,分别是波长λ、镜头角度的正弦值sinθ,以及k1,其中,对于做光刻的人来说,k1这个参数是非常重要的。

缩短波长和加大sinθ(目前可以做到0.93)都可以提升分辨率,但这些都是有代价的,缩短波长λ、增加sinθ,DOF都会缩短,而k3和k1又是有关联的,且比较复杂。

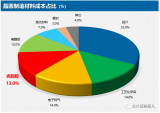

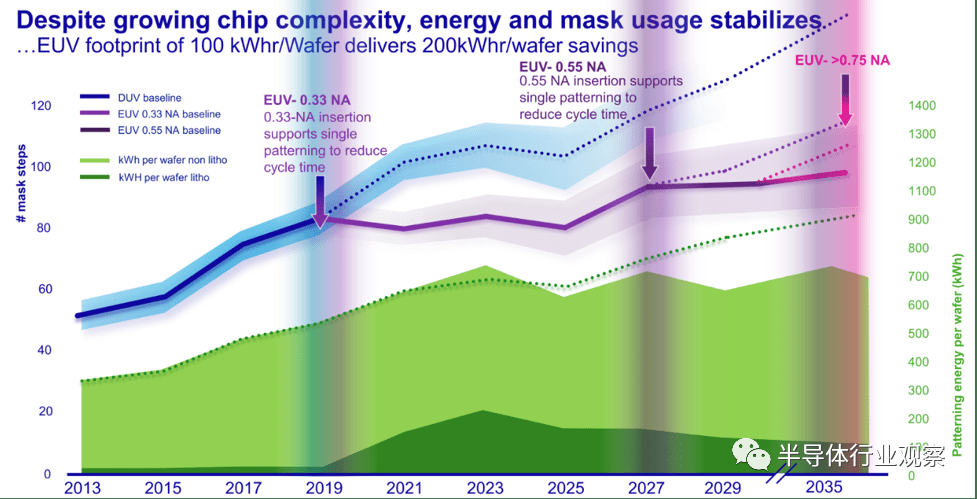

4种方法提升分辨率

对于采用不同设备制造相同制程IC的制造厂来说,其技术水平差异就会很突出,例如,有的厂商用EUV设备(光刻波长为13.5nm)才能做7nm芯片,而有的厂商用DUV设备(光刻波长为193nm)就可以做出7nm芯片,做同样的产品,前者需要更多的投资去购买更新近的设备,而后者则不需要。这就是通过高水平工艺提升分辨率W所产生的经济效益。

1、增大sinθ

如下图所示,依据方程式,有4种方法可以提升分辨率W,而对于工程师来说,其中最方便的方法莫过于增加sinθ了,对于半导体厂的工程师来说,只要向老板多申请一些经费,订购大一点的镜头和机器就好了,因此,工程师会采取的首选方案,往往就是在sinθ上做文章。

提高sinθ的同时,镜头的复杂度随着增加,因为sinθ每增加一点,镜头里就需要增加相应的镜片。以sinθ=0.93的镜头为例,整个镜头的长度会超过一个成年人的身高,而且很重,需要用起重机来搬运和加装。这样的镜头,便宜的也要2000多万美金一个,贵的要7000万美金左右。另外,增加sinθ虽然使工程师轻松不少,但景深DOF的牺牲会比较大。

如下图所示的镜头,左边的5X镜头(0.32NA)是当年在IBM工作时,我的老板发明的,当时,这是全球半导体光刻界最厉害的镜头了。随着技术的进步,新的4X镜头陆续出现,这些镜头里增加了越来越多的镜片,而且对精度的要求逐年提升,要做到波长的五十分之一。

2、减小波长

增加sinθ需要大量的投资,而且越来越贵,此外,目前sinθ已经提升到0.93,已很难再提升,而且其不可能大于1。这样,我们可以通过改变波长λ来进一步提升光刻的分辨率。

但是,改变波长会产生连锁反应,由于镜片对不同波长光的折射率都是不一样的,焦点也就不一样,因此,波长改变一次,就需要对镜片进行矫正,使其焦点正确。但这些对激光的频宽提出了更高的要求,特别是到28nm制程时,传统的光刻光源已经不能满足要求,需要特殊的、更低频宽的激光才能进行矫正。

此外,还有其它一些方法可以矫正焦点,具体如下图所示。

而在将来,更先进的光刻系统内,不允许有任何透光的镜片,如EUV系统,只能通过将光多次反射实现应用功能。

另外,波长每改变一次,光阻也要变,由于光阻是化学性质的,改起来并不容易,特别是当光阻从365变为28的时候,需要很大的改动,实现这一壮举的人是当年我在IBM的同事,当时得到了光刻界的诺贝尔奖,即日本天皇奖,他采用化学放大效应,将光阻提升了十倍,这一技术出来以后,使得整个光刻系统成本下降很多。不过,这种新光阻在刚出来的时候并不稳定,有时能提升十倍,有时又远不能达到这一指标,问题出在哪里呢?经过研究,他最终发现,问题在于光阻的浓度,这就对过滤器提出了很高的要求,需要考虑很多因素,另外,这种过滤器会消耗大量的电能,这对很多应用单位来说,都是不可承受之重。

当波长减小到157nm的时候,装置中的空气会将该波长的光吸收掉,这主要是由氧气造成的,因此,需要一个密封的空间,而且里面不能有氧气,一般是充满氮气,但氮气很难被监测到,且不利于工程师维修(没有氧气,有生命危险)。

当光刻发展到EUV的时候,此时光的波长已经非常小,很容易被装置里面的气体吸收掉,因此,EUV需要抽真空的环境,而要实现真空,整个系统就会变得庞大许多,而且,抽真空泵的震动对光刻系统也会有一定的影响。此外,更加庞大和复杂的系统,维修起来也更加费时费力。

3、减小k1

下面谈k1,对于做光刻的人来说,k1可以说是最有趣的话题了。

k1是一个系数,在显微镜应用当中,k1最小只能降到0.61,再小的话,东西就会模糊,看不清楚了,而在光刻领域,则不存在这个问题,只需要考虑线的位置,只要能曝光就好,因此,可以把k1降低到0.07。通过改变k1,可以不用更换镜片,不用改变波长和光阻,就可以提升分辨率,具有很好的经济效益。此外,DOF还有可能会增加。

减小k1有这么多的好处,但其实现起来并不容易,需要很强的创新思维。

下图,制程工艺为250nm时,那时候的k1=0.63,跟显微镜的差不多,而180nm制程对应的k1则降到了0.47,此时,相对于250nm,线宽比较大,不容易控制,还要考虑很多干扰因素,有很大的学问在里面,需要更多的创新。

k1=0.47的时候,就感觉是一件非常奢侈的事情了,而当制程微缩到130nm的时候,k1进一步降到了0.42,这是一件非常不简单的事情,凝聚了光刻研发工程师的心血和智慧。

当k1=0.63和0.47的时候,是有可能增加DOF的,如下图所示。

4、增大n

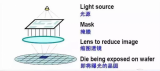

这里的n是折射率,通过改变n,也可以提升光刻系统的分辨率,最简单的方法就是在镜头和晶体之间加入水,以代替空气,也就是沉浸式系统,通过增大n,可以得到短波长的效果。

当NA大于1的时候,特别是1.35NA时,需要放入具有特别构造的镜片,由于涉及到商业机密,下图中没有给出1.35NA的示意图,目前有两家公司可以做到这一点,他们采用不同的方法实现。

下图所示为沉浸式的原理,利用光通过液体介质时会弯折的特性,显微镜的影像透过浸湿的镜头会进一步放大。相反地,当光线通过浸在液体中的微缩影镜头时,就能将影像藉由折射率进一步缩小。

这里用水作为介质是最为经济高效的,否则就需要花几亿美金去研发新的、更好的介质,这样太耗费资金和时间,而且不一定能保证成功,算起来是划不来的。

结语

以上,林本坚博士主要讲述了提升光刻系统分辨率的4种方法,这里凝结了光刻研发工程师的大量心血和智慧,而作为沉浸式光刻技术的发明人,林博士对于产业的技术水平提升和经济效益做出了巨大的贡献。相信随着EUV的到来及普及,更多的先进技术还会诞生,继续把半导体光刻发扬光大。

-

集成电路

+关注

关注

5320文章

10722浏览量

353313 -

半导体

+关注

关注

327文章

24492浏览量

202046 -

光刻技术

+关注

关注

1文章

131浏览量

15642

原文标题:林本坚:把半导体元件缩到光波长的四十分之一

文章出处:【微信号:industry4_0club,微信公众号:工业4俱乐部】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

绕开EUV光刻,下一代纳米压印光刻技术从存储领域开始突围

光刻机的发展历程及工艺流程

光刻胶分类与市场结构

万润股份在半导体制造材料领域稳步推进,涉足光刻胶单体、PI等业务

半导体制造领域光刻胶的作用和意义

什么是光刻工艺?光刻的基本原理

半导体光刻技术及其发展历程,一个详尽立体的光刻世界

半导体光刻技术及其发展历程,一个详尽立体的光刻世界

![[<b class='flag-5'>半导体</b>前端工艺:第三篇] <b class='flag-5'>光刻</b>——<b class='flag-5'>半导体</b>电路的绘制](https://file1.elecfans.com/web2/M00/B1/DB/wKgZomVdgPSAWsXlAAH9_6nQJHk959.png)

评论