2 蜂鸟E203开源SoC

对于一个处理器核,还需要配套的SoC才能具备完整的功能。 蜂鸟E203内核不仅仅完全开源了Core的实现,还搭配完整的开源SoC平台,请参见《蜂鸟E203开源SoC简介》(本篇即将发布,请持续关注公众号;或点击https://github.com/SI-RISCV/e200_opensource 查看详情)了解更多SoC的介绍与信息。

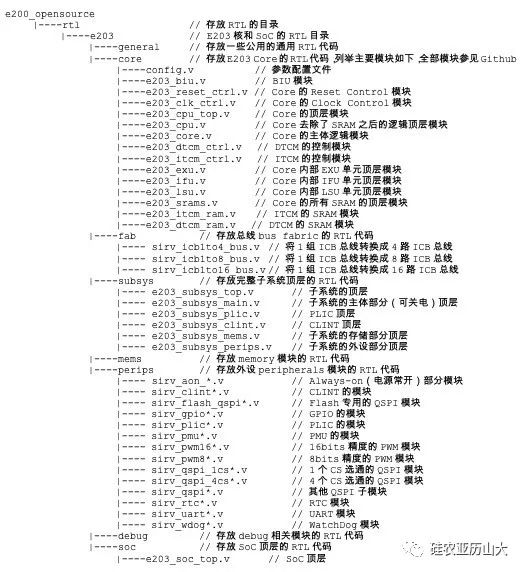

蜂鸟E203开源SoC的代码结构如下所示。

各个主要的代码模块简述如下:

general目录主要用于存放一些通用的Verilog RTL模块供整个SoC公用,譬如一些DFF(D触发器寄存器)定义文件,ICB总线的基础模块等等。

core目录主要用于存放处理器核模块的Verilog RTL代码。e203_cpu_top是蜂鸟E203处理器核的顶层。

fab目录主要实现SoC中ICB Bus Fabric模块的Verilog RTL代码。 sirv_icb1to4_bus.v, sirv_icb1to8_bus.v或者sirv_icb1to16_bus.v实际例化调用了sirv_icb_splt模块将一组ICB总线按照地址区间分发成为4组,8组或者16组ICB总线。

subsys目录包含了SoC的主体顶层模块的Verilog RTL代码,其中e203_subsys_top是事实上的SoC顶层文件,它例化了Main Domain模块(e203_subsys_main.v)和Always-onDomain模块(e203_aon_top.v)。e203_subsys_mems模块实现了系统存储总线(System Memory Bus),通过调用例化sirv_icb1to8_bus模块并且配置其参数的方式来配置每个从设备的地址区间。e203_subsys_perips模块实现了系统设备总线(System Peripheral Bus),通过调用例化sirv_icb1to16_bus模块并且配置其参数的方式来配置每个从设备的地址区间。除了已经实现的从设备,还预留了地址区间实现外部存储(sysmem),外部外设(sysper)和外部快速IO(sysfio)总线接口。

mems目录主要用于存放memory模块的Verilog RTL代码,由于Memory的具体实现依赖于芯片生产加工厂(foundry)譬如SIMC或者TSMC的Memory宏单元,因此本文件夹下的Verilog RTL代码仅仅是行为模型。

perips目录主要用于存放各种外设(Peripherals)模块的Verilog RTL代码,譬如GPIO,UART,SPI等。大部分的Peripherals的Verilog RTL代码是直接复制于SiFive的Freedom E310项目中Chisel语言生成的出的Verilog RTL代码,在此基础上将其TileLink总线接口修改成了ICB总线接口,如图3-5中所示的GPIO模块ICB总线接口。

debug目录包含了SoC中有关debugger调试器模块的Verilog RTL代码。

soc目录主要用于存放SoC顶层模块的Verilog RTL代码。e203_soc_top.v是一个简单地顶层SoC Wrapper模块,将e203_subsys_top进行例化。另外由于e203_subsys_top模块输出的sysmem,sysfio和sysmem总线在此FPGA SoC中并没有连接任何外部从设备。为了防止软件程序访问到这些总线接口的地址区间无任何返回而挂死,在e203_soc_top顶层模块中将这些ICB总线的Command Channel信号直接反接到其Response Channel,同时将Response Channel中的其他返回信号连接成常数0。

3搭建FPGA原型平台

我们为蜂鸟E203开源SoC定制了专用的FPGA原型开发板和JTAG调试器, E203开源项目基于该FPGA开发板,使用蜂鸟E203开源SoC搭建完整的原型平台与示例。

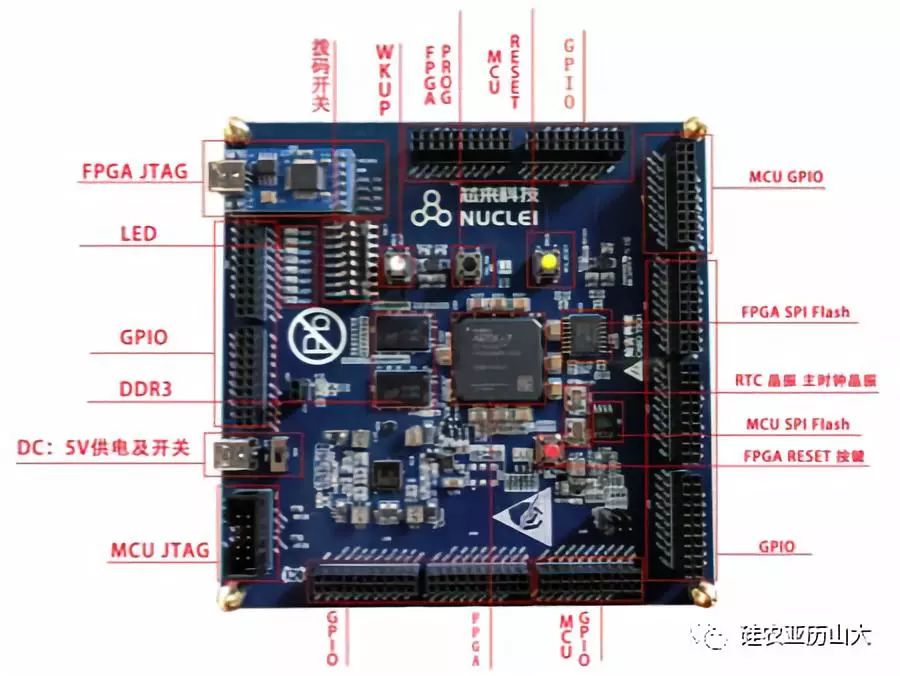

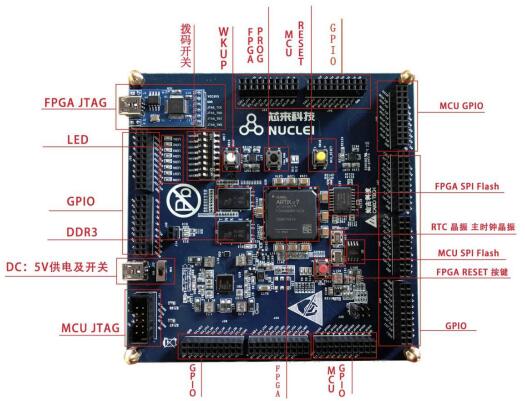

FPGA原型主要分为两部分:FPGA开发板,和调试器。接下来章节分别予以介绍。完整的FPGA开发板原型(包括FPGA开发板和调试器)如图3-1所示。

图3-1 FPGA开发板原型(包括JTAG调试器)

3.1FPGA开发板和项目介绍

蜂鸟E203专用FPGA开发板是一款低成本的入门级XilinxFPGA开发板,如图3-2所示。该开发板不仅可以用于一块FPGA开发板作为电路设计使用,同时由于其预烧了蜂鸟E203开源SoC(包括E203内核),因此其可以直接作为一块MCU SoC原型开发板进行嵌入式软件开发。

有关此FPGA开发板的详细介绍请参见《蜂鸟FPGA开发板和JTAG调试器介绍》。

若想购买此开发板,用户可以在E203开源项目的Github网页上(https://github.com/SI-RISCV/e200_opensource/tree/master/boards)了解此开发板的购买渠道。

图3-2 蜂鸟E203专用FPGA开发板

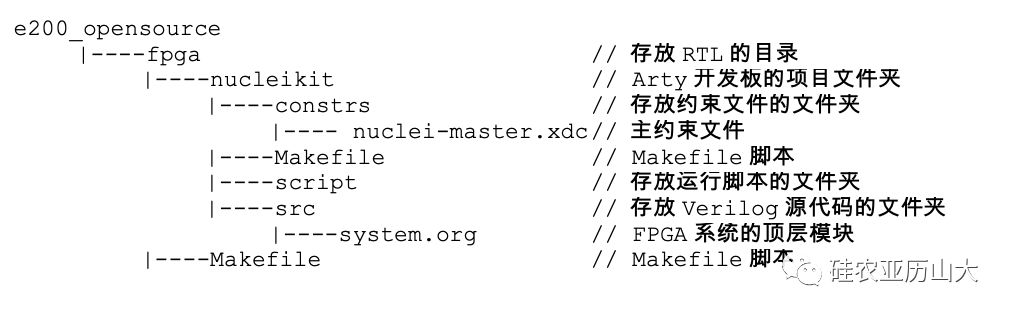

E203开源项目FPGA项目相关的代码结构如下所示。

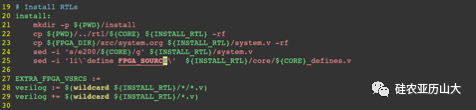

FPGA项目通过Makefile(fpga/common.mk文件)将添加一个特殊的宏FPGA_SOURCE至Core的宏文件中,如图3-3所示。所以最终用于编译FPGA比特流的RTL源代码必须包含此宏(FPGA_SOURCE)。

图3-3 FPGA项目宏定义文件中添加FPGA_SOURCE

在FPGA的顶层模块(system.org)中除了例化SoC的顶层(e203_soc_top)之外,主要是使用Xilinx的I/O Pad单元例化顶层的Pad。另外使用Xilinx的MMCM单元生成时钟。注意:SoC的MainDomain使用的MMCM产生的高速时钟连接到SoC的hfextclk,Always-On Domain使用的是开发板上的低速实时时钟(32.768KHz)。

蜂鸟E203开源SoC的顶层I/O Pad经过FPGA的约束文件(nuclei-master.xdc)进行约束使之连接到FPGA芯片外部的引脚上面(譬如将JTAG I/O约束到开发板的MCU_JTAG插口引脚上)。

3.2生成mcs文件烧写FPGA

在前文中介绍了E203开源项目的SoC整体架构和Verilog RTL代码,为了使得该SoC能够真正运行在FPGA硬件上,需要将其编译成为bitstream文件然后烧录到FPGA中去。可以使用如下步骤进行编译和烧录。

//步骤一:准备好自己的电脑环境,可以在公司的服务器环境中运行,如果是个人用户,推荐如下配置:

(1)使用VMware虚拟机在个人电脑上安装虚拟的Linux操作系统。

(2)由于Linux操作系统的版本众多,推荐使用Ubuntu16.04版本的Linux操作系统有关如何安装VMware以及Ubuntu操作系统本文不做介绍,有关Linux的基本使用本文也不做介绍,请用户自行查阅资料学习。

//步骤二:安装Xilinx Vivado软件至此虚拟机Linux操作系统中。有关如何安装Xilinx Vivado软件本文不做介绍,请用户自行查阅资料了解。

//步骤三:将e200_opensource项目下载到本机Linux环境中,使用如下命令:

git clonehttps://github.com/SI-RISCV/e200_opensource.git

//经过此步骤将项目克隆下来,本机上即可具有如前文所述完整的e200_opensource目录文件夹,假设该目录为

//步骤四:设置需要编译的Core的具体型号,使用如下命令:

cd

//进入到e200_opensource目录文件夹下面的fpga目录。

make install CORE=e203

//运行该命令指明需要为e203内核进行编译,该命令会在fpga目录下生成一个install子文件夹,在其中放置Vivado所需的脚本,且将脚本中的关键字设置为e203。

//步骤五:生成bitstream文件或者mcs文件(推荐使用mcs文件),使用如下命令:

make bit

//运行该命令将调用Vivado软件对VerilogRTL进行编译生成bitstream文件生成的bitstream文件名和路径为

//熟悉Vivado和Xilinx FPGA使用的用户应该了解,bitstream文件烧录到FPGA中去之后FPGA不能掉电,因为一旦掉电之后FPGA烧录的内容即丢失,需要重新使用Vivado的Hardware Manager进行烧录方能使用。

//为了方便用户使用,Xilinx的Arty开发板可以将需要烧录的内容写入开发板上的Flash中,然后在每次FPGA上电之后通过硬件电路自动将需要烧录的内容从外部的Flash中读出并烧录到FPGA之中(该过程非常的快,不影响用户使用)。由于Flash是非易失性的内存,具有掉电后仍可保存的特性,因此意味着将需要烧录的内容写入Flash后,每次掉电后无需使用Hardware Manager人工重新烧录(而是硬件电路快速自动完成),即等效于,FPGA上电即可使用。有关此特性的详细原理与描述,本文不做赘述,请用户自行参阅Arty开发板手册。

//为了能够将烧录FPGA的内容写入Flash中,需要生成mcs文件,使用如下命令:

make mcs

//运行该命令将调用Vivado软件对VerilogRTL进行编译生成mcs文件生成的mcs文件名和路径为

如何使用Vivado的HardwareManager烧写mcs文件至FPGA开发板上的Flash中去,参考如下步骤。

//前提步骤1:将FPGA开发板的“FPGA JTAG接口”通过USB连接线与电脑的USB接口连接。开发板的“FPGA JTAG接口”的位置请参见图3-2中标注所示。

//前提步骤2:将FPGA开发板的“DC:5V供电及开关”通过USB连接线与电脑USB接口或者电源插座连接,并将“开关”拨开,对FPGA开发板进行供电。开发板的“DC:5V供电及开关”的位置请参见图3-2中标注所示。

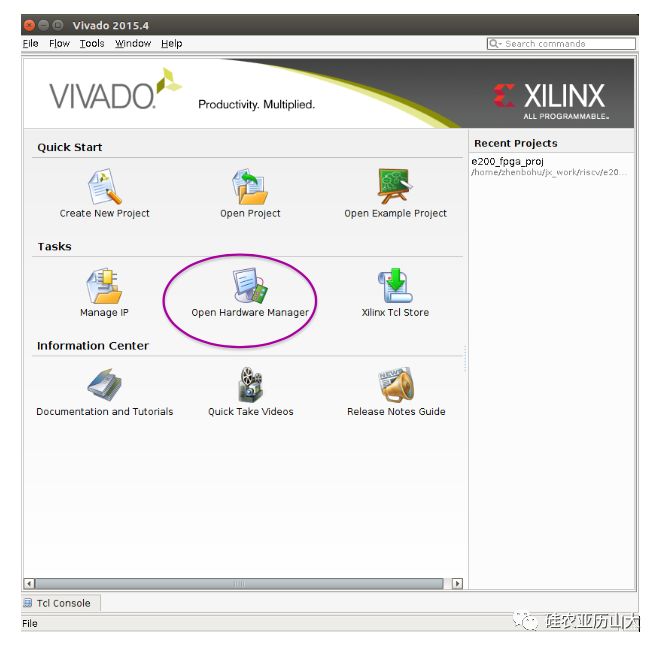

//步骤一:打开Vivado软件。

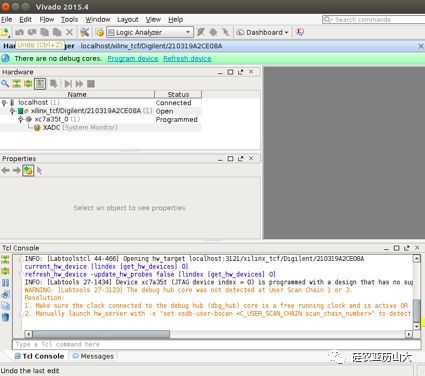

//步骤二:打开Hardware Manager,会自动连接FPGA开发板(如果前提步骤1操作正确)。如图3-4和图3-5所示。

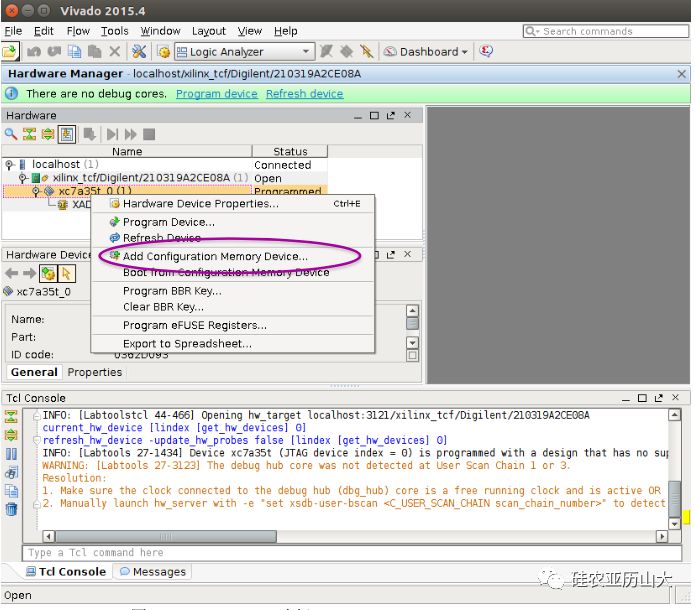

//步骤三:右键FPGA Device,选择“Add Configuration Memory Device”。如图3-6所示。

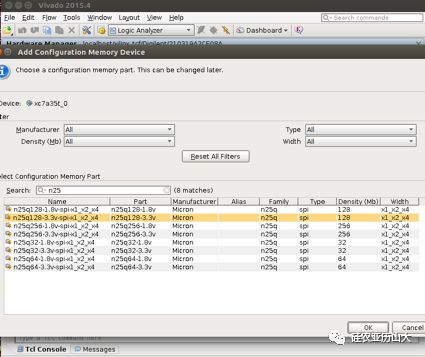

//步骤四:选择如下参数的Flash,如图3-7所示:

Part n25q128-3.3v

Manufacturer Micron

Family n25q

Type spi

Density 128

Width x1 x2 x4

//步骤五:弹出“Do you want to program the configuration memory device now?”,选择OK

//步骤六:在弹出的窗口中的

//步骤七:一旦烧写Flash成功,则可以通过按开发板上的“FPGA_PROG”按键触发硬件电路使用Flash中的内容对FPGA重新进行烧录。

注意:FPGA烧写成功之后,则可以无需再连接“FPGA JTAG接口”的USB连接线。

图3-4打开Vivado Hardware Manager

图3-5使用Vivado Hardware Manager连接Arty开发板

图3-6 FPGA Device选择AddConfiguration Memory Device

图3-7 选择Flash类型

3.3JTAG调试器

图3-8 蜂鸟E203专用FPGA开发板的MCU_JTAG插槽

为了支持使用GDB进行交互式调试或者通过GDB动态下载程序到处理器中运行,需要为FPGA原型平台配备一个JTAG调试器(JTAG Debugger),E203内核支持通过标准的JTAG接口对其进行调试,且SoC顶层JTAG的I/O Pad连接到了 FPGA芯片的pin脚上,而该组pin脚在E203专用FPGA开发板上实际被连接到MCU_JTAG插槽上,如图3-8中黄色圆圈所示。

我们为E203内核定制了专用的“JTAG调试器”,如图3-9中黄色圆圈所示。

图3-9 蜂鸟E203专用的JTAG调试器

有关此JTAG调试器的详细介绍请参见《蜂鸟FPGA开发板和JTAG调试器介绍》。

若想购买此JTAG调试器,用户可以在E203开源项目的Github网页上(https://github.com/SI-RISCV/e200_opensource/tree/master/boards)了解此JTAG调试器的购买渠道。

由于“JTAG调试器”将其与上游主机PC的USB接口连接,因此上游PC的USB端口需要正确的设置以保证其有正确的权限。以Ubuntu 16.04为例,可以使用如下步骤进行配置。

//步骤一:准备好自己的电脑环境,可以在公司的服务器环境中运行,如果是个人用户,推荐如下配置:

(1)使用VMware虚拟机在个人电脑上安装虚拟的Linux操作系统。

(2)由于Linux操作系统的版本众多,推荐使用Ubuntu16.04版本的Linux操作系统有关如何安装VMware以及Ubuntu操作系统本文不做介绍,有关Linux的基本使用本文也不做介绍,请用户自行查阅资料学习。

//步骤二:使用“JTAG调试器”将主机PC与FPGA开发板连接,如图4-9中圆圈所示。注意使该USB接口被虚拟机的Linux系统识别(而非被Windows识别),如图4-10中圆圈所示,若USB图标在虚拟机中显示为高亮,则表明USB被虚拟机中Linux系统正确识别(而非被Windows识别),将FPGA开发板通电。

//步骤三:使用如下命令查看USB设备的状态:

lsusb //运行该命令后会显示如下信息。

...

Bus 001Device 029: ID 15ba:002a Olimex Ltd. ARM-USB-TINY-H JTAG interface

//步骤四:使用如下命令设置udev rules使得该USB设备能够被plugdev group所访问:

sudo vi /etc/udev/rules.d/99-openocd.rules

//用vi打开该文件,然后添加以下内容至该文件中,然后保存退出。

# These arefor the Olimex Debugger for use with Arty Dev Kit

SUBSYSTEM=="usb",ATTR{idVendor}=="15ba",

ATTR{idProduct}=="002a",MODE="664", GROUP="plugdev"

SUBSYSTEM=="tty",ATTRS{idVendor}=="15ba",

ATTRS{idProduct}=="002a",MODE="664", GROUP="plugdev"

//步骤五:使用如下命令查看该USB设备是否属于plugdev group:

ls /dev/ttyUSB* //运行该命令后会显示类似如下信息。

/dev/ttyUSB0/dev/ttyUSB1

ls -l/dev/ttyUSB1 //运行该命令后会显示类似如下信息。

crw-rw-r-- 1root plugdev 188, 1 Nov 28 12:53 /dev/ttyUSB1

//步骤六:将你自己的用户添加到plugdev group中:

whoami

//运行该命令能显示自己用户名,假设你的自己用户名显示为your_user_name。运行如下命令将your_user_name添加到plugdev group中sudo usermod -a -G plugdev your user name。

//步骤七:确认自己的用户是否属于plugdev group:

groups //运行该命令后会显示类似如下信息。

... plugdev...

//只要从显示的groups中看到plugdev则意味着自己的用户属于该组,表示设置成功 。

图3-10 虚拟机Linux系统识别USB图标

在下一章将介绍利用该JTAG调试器如何使用GDB软件对蜂鸟E203 SoC原型进行程序下载或远程调试。

3.4 FPGA原型平台DIY总结

至此,我们将以上论述的加以总结,为了能够搭建完整的FPGA原型平台,用户需要做如下硬件的准备:

购买一块蜂鸟E203专用FPGA开发板

购买一块蜂鸟E203专用JTAG调试器

用户需要做如下软件的准备:

推荐安装VMware虚拟机且安装Linux操作系统于虚拟机中

安装Xilinx的Vivado软件

在下一章将介绍如何使用烧录后的FPGA原型平台运行真正的软件示例。

-

FPGA

+关注

关注

1599文章

21270浏览量

592789 -

开发板

+关注

关注

25文章

4396浏览量

93750

原文标题:蜂鸟FPGA开发板全知道篇2:快速上手介绍(中)

文章出处:【微信号:real_farmer,微信公众号:硅农亚历山大】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

MYMINIEYE Runber蜂鸟开发版免费试用

【MYMINIEYE Runber蜂鸟开发版免费试用连载】国产FPGA试用评测之MYMINIEYE Runber蜂鸟开发板

【MYMINIEYE Runber蜂鸟开发版免费试用连载】高云FPGA开箱

【RSIC-V】Lab1:蜂鸟e203上手教程

【RSIC-V】Lab1:蜂鸟e203上手教程

在Picorv32 / 蜂鸟E203软核上运行RT-Thread的设计实现

将蜂鸟E203烧至开发板后,在NucleiStudio上跑hello_world报错怎么解决?

Ubuntu环境下将蜂鸟e203的hello_world例程下载到开发板上,遇到JTAG问题求解答

求助,如何解决J-Link调试蜂鸟E203失败的问题?

使用RVSTAR开发板的常见问题

蜂鸟FPGA开发板及JTAG下载器详细说明

蜂鸟FPGA开发板和JTAG调试器介绍

蜂鸟FPGA开发板及蜂鸟JTAG下载器讲解说明

蜂鸟FPGA开发板及蜂鸟JTAG下载器讲解说明

评论