声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

32文章

1794浏览量

130489 -

优化

+关注

关注

0文章

220浏览量

23707 -

Vivado

+关注

关注

18文章

785浏览量

65079

发布评论请先 登录

相关推荐

Vivado编译常见错误与关键警告梳理与解析

Xilinx Vivado开发环境编译HDL时,对时钟信号设置了编译规则,如果时钟由于硬件设计原因分配到了普通IO上,而非_SRCC或者_MRCC专用时钟管脚上时,编译器就会提示错误。

如何禁止vivado自动生成 bufg

定和可靠。Vivado在编译设计过程中会自动检测到时钟信号,并自动生成BUFG来缓冲时钟。然而,在某些情况下,我们可能希望手动管理时钟信号。 要禁止Vivado自动生成BUFG,可以按照以下步骤进行

Vivado那些事儿:节省编译时间系列文章

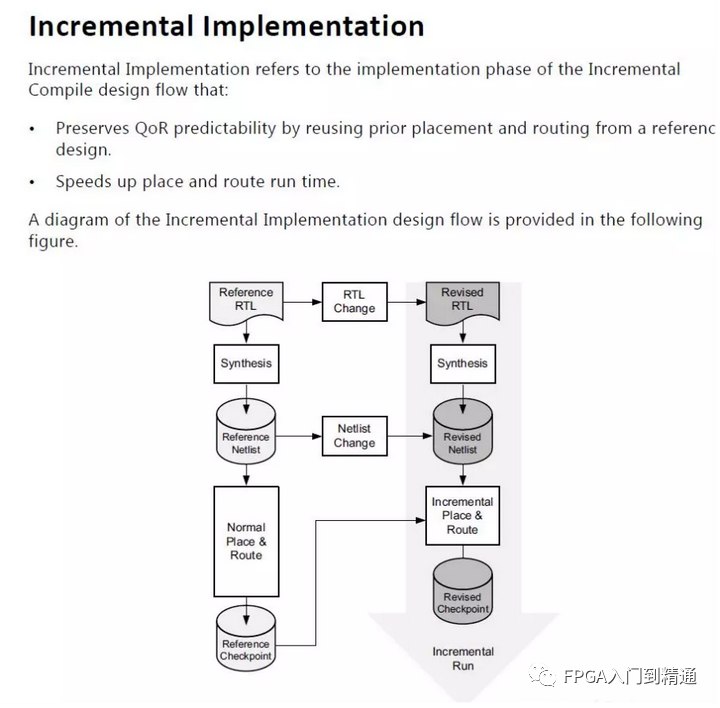

虽然想必您知道,在综合或实现阶段,增量运行可以从参考文件中读取和复制信息,但仅在某些阶段中能节省时间,如果网表发生大量更改,其中引用的内容就会减少,编译时间也会受到相应影响。

Vivado Design Suite教程:动态功能交换

电子发烧友网站提供《Vivado Design Suite教程:动态功能交换.pdf》资料免费下载

发表于 09-14 15:13

•0次下载

Vivado设计套件用户:使用Vivado IDE的指南

电子发烧友网站提供《Vivado设计套件用户:使用Vivado IDE的指南.pdf》资料免费下载

发表于 09-13 15:25

•5次下载

Xilinx Vivado使用增量实现

增量实现自从首次获得支持以来,不断升级演变,在此过程中已添加了多项针对性能和编译时间的增强功能。它解决了实现阶段针对快速迭代的需求,显著节省了编译时间,还能确保所得结果和性能的可预测性

用 TCL 定制 Vivado 设计实现流程

迭代运行,但需留意每次的时序报告,若出现时序恶化就应及时停止。

增量设计流程

Vivado 中的增量设计也是一个不得不提的功能。当设计进行到后期,每次运行改动很小,在开始后端实现前读

发表于 06-28 19:34

Vivado增量编译的基本概念、优点、使用方法以及注意事项

随着FPGA设计的复杂度不断提高,设计人员需要选择更为高效的设计流程来保证开发效率和减少开发成本。其中,Vivado增量编译是一种非常重要的设计流程。本文将介绍Vivado

Vivado Design Suite 用户指南介绍

DFX 是由多个部分组成的综合性解决方案。这些要素包括:AMD 芯片能进行动态重配置,Vivado 软件流程支持编译设计(从 RTL 到比特流),以及各种补充性功能特性(如 IP)。

发表于 05-18 09:47

•512次阅读

在Vivado中实现ECO功能

关于 Tcl 在 Vivado中的应用文章从 Tcl 的基本语法和在 Vivado 中的 应用展开,继上篇《用 Tcl 定制 Vivado 设计实现流程》介绍了如何扩展甚 至是定制 FPGA

Vivado 2015.3的新增量编译功能

Vivado 2015.3的新增量编译功能

评论