声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

32文章

1794浏览量

130513 -

存储

+关注

关注

12文章

3854浏览量

84656 -

开源

+关注

关注

3文章

2985浏览量

41716

发布评论请先 登录

相关推荐

苹果为遵守《数字市场法》,调整iOS、App Store及Safari功能

即将与Apple团队进行面对面会议,讨论欧盟《数字市场法》对其正在欧盟分发的App所带来的影响及iOS、Safari及其App Store的变革。咨询的重点内容涵盖iOS上的其他分发渠道、App Store上的支付手段、网页购买链接的建立以及新的商业条款等。

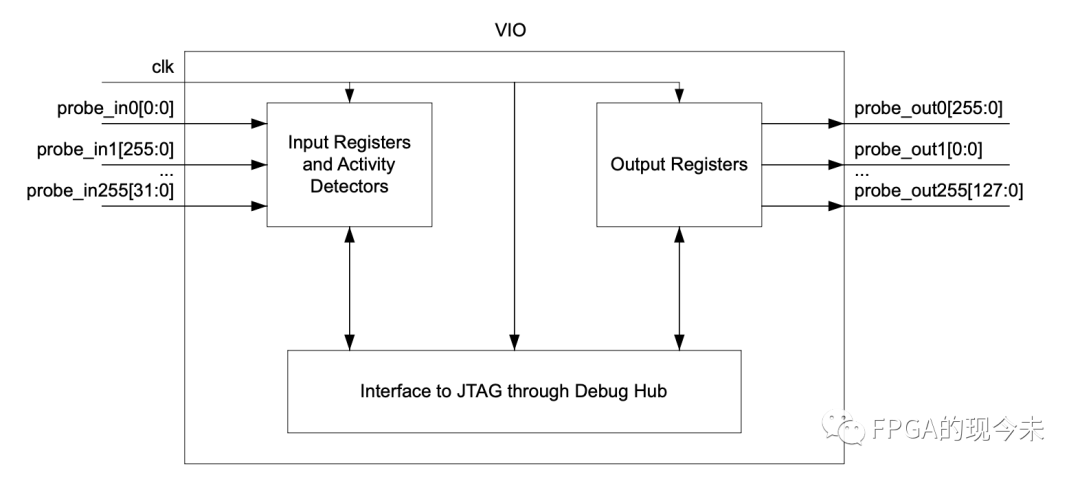

Xilinx VIO介绍和应用场景

在以往的项目中,要控制FPGA内部某个信号的值,往往是通过配置寄存器来实现的。其实Xilinx还提供了一个叫VIO的core,可以动态改变FPGA内部某个信号的值,但是一直没有用过,一来对于以前的项目来说,没有应用场景,通过寄存器就可以配置了;二来感觉这个东西不是很“实用”。

简述Xilinx 7系列FPGA芯片相关知识

Xilinx 7系列 芯片 应用非常广泛,具有成本低、性能强悍、成熟稳定的特点,目前Xilinx( AMD )已延长该系列芯片的生命周期至少到2035年。 本文主要介绍Xilinx 7

Xilinx FPGA的GTx的参考时钟

本文主要介绍Xilinx FPGA的GTx的参考时钟。下面就从参考时钟的模式、参考时钟的选择等方面进行介绍。

发表于 09-15 09:14

•2396次阅读

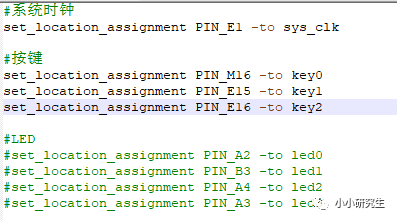

基于Xilinx FPGA的边界扫描应用

上一篇文章,介绍了基于STM32F103的JTAG边界扫描应用,演示了TopJTAG Probe软件的应用,以及边界扫描的基本功能。本文介绍基于Xilinx FPGA的边界扫描应用,两者几乎是一样。

Arm Cortex-M1 DesignStart FPGA Xilinx版用户指南

适用于需要将小型处理器集成到FPGA中的深度嵌入式应用。

该处理器实现ARMv6-M架构,并与用于ASIC实现的Cortex-M0和Cortex-M0+处理器密切相关。

本章介绍了Cortex-M1 DesignStart FPGA-Xilinx版的功能和目录结构。

发表于 08-16 06:10

Xilinx Vivado DDS IP使用方法

DDS(Direct Digital Frequency Synthesizer) 直接数字频率合成器,本文主要介绍如何调用Xilinx的DDS IP核生成某一频率的Sin和Cos信号。

TCL发布碳中和白皮书 官宣“3050”碳中和目标及行动计划

在发布仪式上,tcl科技集团首席运营官王成从企业绿色发展、构建绿色生态及体现社会价值等方面介绍了碳中和实践案例。他介绍说,以对企业碳排放现状的数据分析和科学计划为基础,tcl构建了碳排

用 TCL 定制 Vivado 设计实现流程

今天推出Xilinx已发布的《Vivado使用误区与进阶》系列:用TCL定制Vivado设计实现流程。

上一篇《Tcl 在 Vivado 中的应用》介绍了

发表于 06-28 19:34

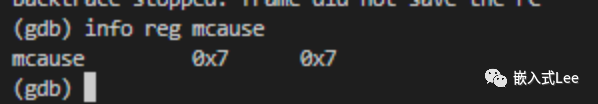

RISC-V的Store AMO access fault调试实例

本文以一个实例分享RISC-V的Store AMO access fault异常的调试过程。Store AMO access fault主要发生在非法地址访问时(栈溢出,指针异常等)。

Xilinx Tcl Store的基本介绍

Xilinx Tcl Store的基本介绍

评论