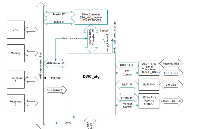

如果嵌入式 IP 目录以及 AXI USB 2.0 器件 IP 对您来说比较陌生的话,此视频将向您详细地介绍这两者。通过本次培训您将学习到 AXI USB2.0器件的关键性能、配置选项以及基本架构,同时还包括有如何在大容量存储应用中使用AXI USB 2.0器件IP的典型应用案例。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

usb

+关注

关注

59文章

7413浏览量

257881 -

赛灵思

+关注

关注

32文章

1794浏览量

130497 -

IP

+关注

关注

5文章

1399浏览量

148262

发布评论请先 登录

相关推荐

XILINX FPGA IP之AXI Traffic Generator

AXI Traffic Generator IP 用于在AXI4和AXI4-Stream互连以及其他AXI4系统外设上生成特定序列(流量)。

LogiCORE IP AXI UART 16550内核简介

LogiCORE IP AXI 通用异步接收发送器 (UART) 16550 连接到高级微控制器总线架构 (AMBA) AXI,为异步串行数据传输提供控制器接口。该软 IP 核旨在通过

LogiCORE JTAG至AXI Master IP核简介

LogiCORE JTAG至AXI Master IP核是一个可定制的核,可生成AXIAXI总线可用于处理和驱动系统中FPGA内部的AXI信号。AXI总线接口协议可通过

什么是AXI?AXI如何工作?

Xilinx 从 Spartan-6 和 Virtex-6 器件开始采用高级可扩展接口 (AXI) 协议作为知识产权 (IP) 内核。Xilinx 继续将 AXI 协议用于针对 7 系

LogiCORE IP AXI4-Stream FIFO内核解决方案

LogiCORE IP AXI4-Stream FIFO内核允许以内存映射方式访问一个AXI4-Stream接口。该内核可用于与AXI4-Stream

AMBA3.0 AXI总线接口协议的研究与应用

本文介绍了AMBA3.0AXI的结构和特点,分析了新的AMBA3.0AXI协议相对于AMBA2.0的优点。它将革新未来高性能SOC总线互连技术,其特点使它更加适合未来的高性能、低延迟设

发表于 09-20 08:30

USB IP介绍

符合USB2.0中的全速规范• 可用资源:8个双向端点• 支持四种传输类型• 对于bulk和同步传输,还支持double buffer模式;使得一个buffer用于USB硬件和PC交换数据的同时

发表于 09-12 08:24

IP_数据表(I-10):USB2.0 Transceiver for TSMC 28nm HPC+

IP_数据表(I-10):USB2.0 Transceiver for TSMC 28nm HPC+

发表于 07-06 20:21

•0次下载

IP_数据表(I-9):USB2.0 Transceiver for TSMC 40nm LP

IP_数据表(I-9):USB2.0 Transceiver for TSMC 40nm LP

发表于 07-06 20:12

•0次下载

IP_数据表(I-26):USB2.0 Transceiver for Samsung 28nm

IP_数据表(I-26):USB2.0 Transceiver for Samsung 28nm

发表于 07-05 19:45

•0次下载

自定义AXI-Lite接口的IP及源码分析

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制,后面对 Xilinx 提供的整个

发表于 06-25 16:31

•2031次阅读

简单讲解AXI Interconnect IP核的使用方法

最近需要用到AXI接口的模块,xilinx的IP核很多都用到了AXI总线进行数据和指令传输。如果有多个设备需要使用AXI协议对AXI接口的B

Video In to AXI4-Stream IP核知识介绍

大家好!今日分享一些关于Video In to AXI4-Stream IP 核的知识。在具体学习IP核的过程中,我也将分享一些关于如何看xilinx英文文档的技巧。

基于DWC2的USB驱动开发-0x02 DWC2 USB2.0 IP功能特征介绍

DWC2即新思(Synopsys )的DesignWare® Cores USB 2.0 HiSpeed On-The-Go (OTG)控制器IP,被大量使用。从linux的内核源码驱动中就带DWC2的驱动(新思官方维护),可以

AXI USB 2.0器件IP及嵌入式IP目录介绍

AXI USB 2.0器件IP及嵌入式IP目录介绍

评论