Virtex®-7 2000T拥有 68 亿个晶体管, 200 万个逻辑单元,相当于 2,000 万个 ASIC 门。这也是首款采用赛灵思独特的堆叠硅片互联(SSI)技术的FPGA。Virtex-7 2000T将使其无需借助并行或者串行I/O, 或者通过片外的 PCB连线与相邻的 FPGA 互联, 即可充分享受到FPGA芯片内高带宽、低时延、低功耗互联机制的优势。

了解如何将复杂的SoC平台映射到单个Virtex®-7 2000T FPGA

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21309浏览量

593130 -

赛灵思

+关注

关注

32文章

1794浏览量

130513 -

soc

+关注

关注

38文章

3743浏览量

215659

发布评论请先 登录

相关推荐

中高端FPGA如何选择

为了使数据传输更加高效,Achronix FPGA上的Memory资源也是非常给力,不管是片上Ram还是DDR接口,都比Virtex Ultrascale+有很大优势。

发表于 04-24 15:09

TC33X将dCache映射到RAM会导致存储总线错误是为什么?如何解决?

我尝试通过以下(简化的)顺序使用 TC33X 将数据缓存映射到 RAM 区域:

CPU_DCON0 = 2

MTU_CLC = 0 MTU_MEMMAP |= 1

在软件闪烁且调试器保持连接

发表于 01-25 06:23

如何将共享代码映射到DSPR5以及将其映射到其他RAM区域?

Scratch-Pad Sram(CPU5 DSPR)相关联。 在链接器脚本中,我已经映射了每个.text 部分移至其各自的 PSPR 内核。 我想知道如何将共享代码映射到 DSPR5 以及

发表于 01-24 07:26

使用AD9690时数据具体是怎样映射到串行链路上的?

您好:

使用AD9690时,想知道数据具体是怎样映射到串行链路上的。

我打算不使用AD9690内置的DDC,直接将采样后的一路数据通过串行链路传递到FPGA;在手册中看到一幅图描述着,一个采样点的高

发表于 12-12 08:22

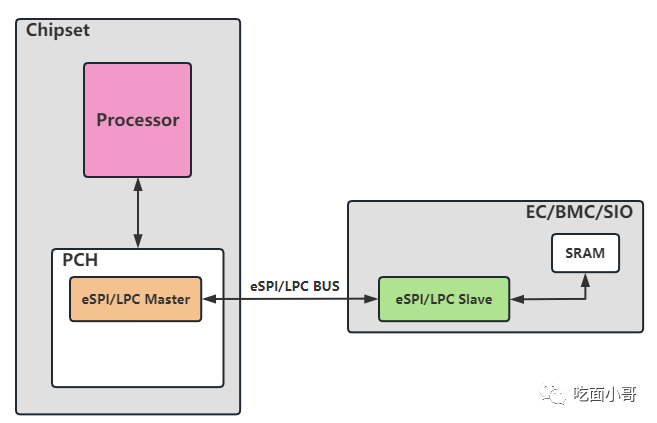

EC SRAM映射到CPU Memory空间的共享内存设计

ShareMemory,顾名思义就是共享内存。这个概念在很多计算机系统中都存在,本文特指 EC SRAM 映射到 CPU Memory 空间的共享内存设计。

如何将Arm Cortex-M处理器与Xilinx的FPGA和SoC结合使用

电子发烧友网站提供《如何将Arm Cortex-M处理器与Xilinx的FPGA和SoC结合使用.pdf》资料免费下载

发表于 09-15 15:04

•1次下载

ARM用于A级系统的地址映射

本文档描述了ARM用于A级系统的地址映射,来自模型和模拟器到开发板和复杂的SoC。

它解释了存储器、外围设备和扩展的地址分区选择空间。

它描述了当32位平台操作系统使用36位或40位地

发表于 08-02 08:19

多片FPGA原型验证的限制因素有哪些?

当SoC系统的规模很大的时候,单片FPGA验证平台已经无法容纳这么多容量,我们将采取将SoC设计划分为多个FPGA的

发表于 06-19 15:42

•562次阅读

多片FPGA原型的两种分割方式介绍

综合工具的任务是将SoC设计映射到可用的FPGA资源中。自动化程度越高,构建基于FPGA的原型的过程就越容易、越快。

发表于 06-13 09:27

•317次阅读

在evk套件mimxrt1024上的lwip ping演示示例中,如何将其映射到enet中断114的微控制器编号?

在 evk 套件 mimxrt1024 上的 lwip ping 演示示例中。Gpio1 22 用作 enet 的中断引脚。如何将其映射到 enet 中断 114 的微控制器编号。gpio1 4 也用于重置,但我没有看到任何地方

发表于 05-22 08:39

如何将缓存内存映射为快速堆?

我有特殊的算法代码,经过优化可以在快速 RAM 上运行得快很多倍。

是否可以将 iMX8mm SoC 的 L1 或 L2 缓存的部分映射到特殊内存地址以将其用作快速堆内存?

这样的事情

发表于 05-18 11:48

如何将这些SoC的逻辑功能原型正确的移植到多片FPGA中?

当SoC的规模在一片FPGA中装不下的时候,我们通常选择多片FPGA原型验证的平台来承载整个SoC系统。

发表于 05-10 10:15

•198次阅读

如何将复杂的SoC平台映射到单个Virtex-7 2000T FPGA上

如何将复杂的SoC平台映射到单个Virtex-7 2000T FPGA上

评论