本视频将介绍 Xilinx PCIe DMA 子系统的设置过程与性能测试,先展示可实现的硬件性能,然后说明用软件进行实际传输怎么会影响性能。最后将讨论不同的选项,以提高包括选择最佳传输量与轮询在内的性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

32文章

1794浏览量

130513 -

硬件

+关注

关注

11文章

2922浏览量

64755 -

PCIe

+关注

关注

13文章

1083浏览量

80811

发布评论请先 登录

相关推荐

高性能NVMe主机控制器,Xilinx FPGA PCIe 3

SEQ128K Q32T1测试模式下的读写性能。针对多路数据通道访问PCIe SSD,使用NVMe的多队列特性,NVMe Host Controller IP支持灵活配置DMA读写的通

发表于 04-20 14:41

高性能NVMe主机控制器,Xilinx FPGA NVMe Host Accelerator IP

的读写性能。针对多路数据通道访问PCIe SSD,使用NVMe的多队列特性,NVMe Host Controller IP支持灵活配置DMA读写的通道个数,按照NVMe队列优先级仲裁(循环仲裁或加权

发表于 04-10 22:55

Xilinx FPGA高性能NVMe SSD主机控制器,NVMe Host Controller IP

的读写性能。针对多路数据通道访问PCIe SSD,使用NVMe的多队列特性,NVMe Host Controller IP支持灵活配置DMA读写的通道个数,按照NVMe队列优先级仲裁(循环仲裁或加权

发表于 03-27 17:23

8路SDI/HDMI/MIPI/PCIe-DMA音视频采集,V4L2驱动应用介绍

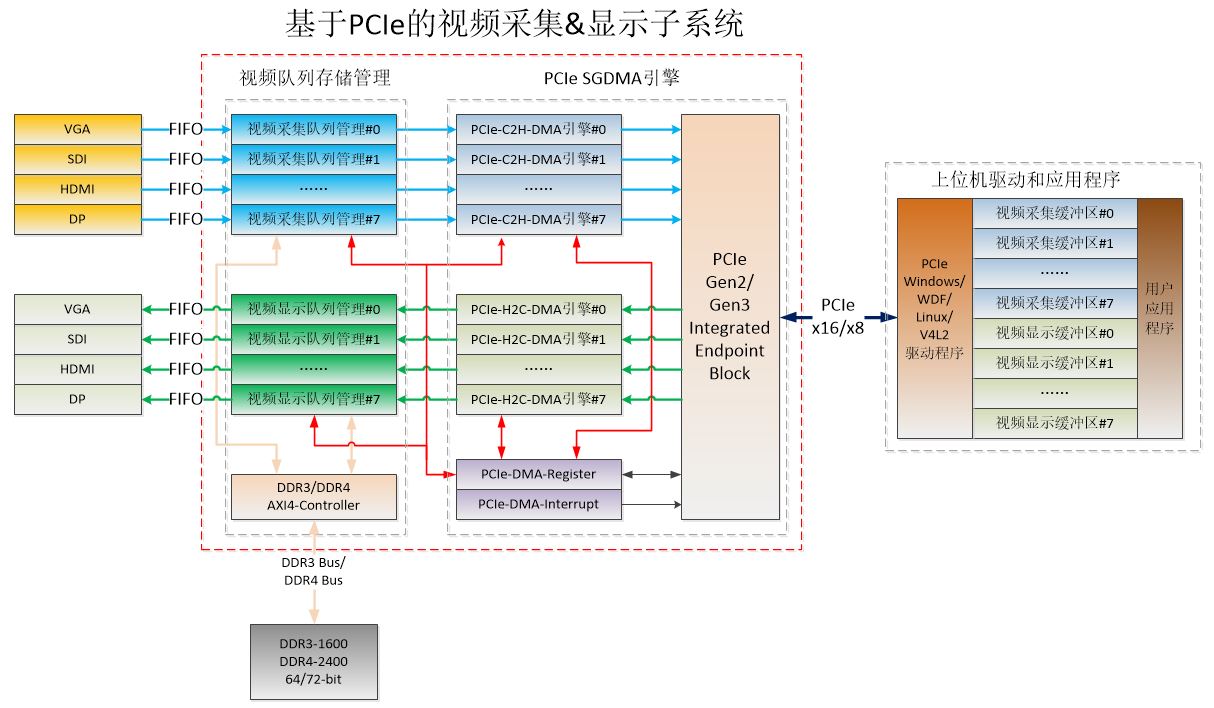

基于PCIe的多路视频采集与显示子系统1 概述视频采集与显示子系统可以实时采集多路视频信号,并存储到视频采集队列中,借助高效的硬实时视频帧出入队列管理和PCIe C2H

发表于 03-13 13:59

Xilinx FPGA NVMe主机控制器IP,高性能版本介绍应用

,NVMe Host Controller IP所消耗的BRAM比较多,可以达到CrystalDiskMark测试软件SEQ128K Q32T1测试模式下的读写性能。针对多路数据通道访问PCI

发表于 03-09 13:56

Xilinx FPGA 1/4/8通道PCIe-DMA控制器IP,高性能应用介绍

提供的信息:源地址,目的地址和传输数据长度,Multi-Channel PCIe QDMA&RDMA Subsystem实现Host存储器和PCIe DMA子系统之间的数据搬移

发表于 03-07 13:54

V4L2视频采集,基于PCIe的多路视频采集与显示子系统

视频采集与显示子系统可以实时采集多路视频信号,并存储到视频采集队列中,借助高效的硬实时视频帧出入队列管理和PCIe C2H DMA引擎,将采集到的视频帧实时传递到上位机采集缓冲区。在超带宽视频采集

Xilinx高性能PCIe DMA控制器IP,8个DMA通道

基于PCI Express Integrated Block,Multi-Channel PCIe QDMA Subsystem实现了使用DMA地址队列的独立多通道、高性能Continous

Xilinx FPGA NVMe Host Controller IP,NVMe主机控制器

128K-Byte,NVMe Host Controller IP所消耗的BRAM比较多,可以达到CrystalDiskMark测试软件SEQ128K Q32T1测试模式下的读写性能。

针对多路数据通道访问

发表于 02-21 10:16

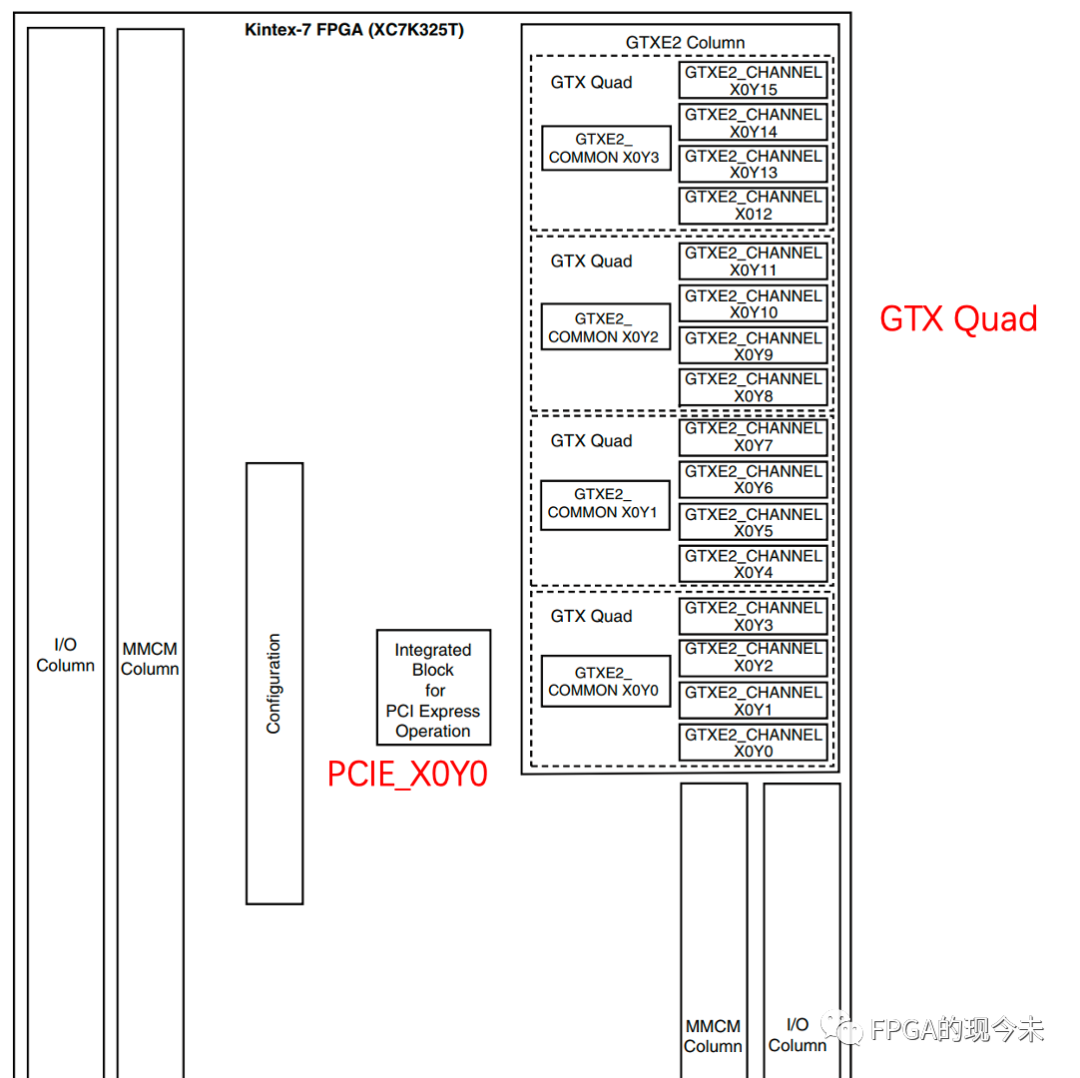

Xilinx PCIE core管脚分配错误的解决方案

最近弄PCIE,遇到一个问题,以前我们总认为:Xilinx的PCIE core的管脚是固定的,即指定了PCIE core的位置,对应的管脚也就指定了,真实情况是怎么样的呢?

关于xilinx FPGA pcie测试问题

FPGA pcie dma测试

流程:金手指和电脑连接之后,先加载程序,pc重启;

现象:pc无法开机。

FPGA pcie x8,pc x16,直接连接上去的

请问这是什么情况呀,为

发表于 09-13 18:21

全爱科技Atlas200I A2 AI加速模块-FPGA PCIE接口验证平台

Xilinx的官方PCIE 2.0 IP核或0 IP核,用来实现PCIE 硬核IP的例化;

使用DMA控制器,实现PCIE

发表于 09-05 14:39

基于FPGA的PCIE通信测试

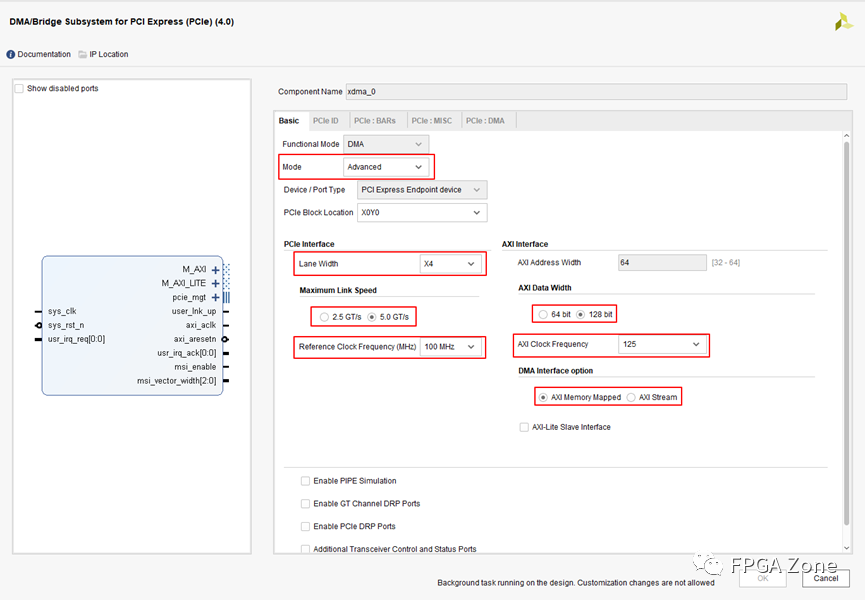

本文介绍一个FPGA开源项目:PCIE通信。该工程围绕Vivado软件中提供的PCIE通信IP核XDMA IP建立。Xilinx提供了XDMA的开源驱动程序,可在Windows系统或者

如何使用TMT4 PCIe性能综合测试仪创建PCIe参考模板?(附白皮书下载)

点击上方 “泰克科技” 关注我们! 引言 随着用于 PCIe 链路健康状况测试的TMT4 PCIe性能综合测试仪的推出,出现了一个问题,即确

Xilinx PCIe DMA子系统的性能测试

Xilinx PCIe DMA子系统的性能测试

评论