System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用。或者直接生成比特流下载文件。能够加快DSP系统的开发进度。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

544文章

7681浏览量

344331 -

赛灵思

+关注

关注

32文章

1794浏览量

130510 -

仿真

+关注

关注

50文章

3872浏览量

132147

发布评论请先 登录

相关推荐

如何在测试中使用ChatGPT

Dimitar Panayotov 在 2023 年 QA Challenge Accepted 大会 上分享了他如何在测试中使用 ChatGPT。

如何在运行时计算设计中使用的时钟频率?

我想知道如何在运行时计算设计中使用的时钟频率(设计使用时钟组件),尤其是组件内部的时钟,例如 UART。

例如,使用 clock_getS

发表于 01-24 06:09

fpga与dsp通讯怎样同步时钟频率?dsp和fpga通信如何测试?

或丢失。 为了实现FPGA和DSP的同步时钟频率,可以采用以下两种方式: 1. 外部时钟源同步 通过引入外部时钟源,让FPGA和

安装System Generator时System Generator for DSP这个选项没有出现怎么办?

各位大佬,我在安装System Generator时,跟着教程走,发现在vivado中没有出现System Generator for DSP

发表于 09-26 21:54

如何在Vitis HLS GUI中使用库函数?

Vitis™ HLS 2023.1 支持新的 L1 库向导,本文将讲解如何下载 L1 库、查看所有可用功能以及如何在 Vitis HLS GUI 中使用库函数。

CoreLink™ADB-400AMBA®域桥接循环模型用户指南

AMBA®域桥(ADB)在AMBA系统中集成了多个电源或时钟域,或不同的电压电平。它提供了两个组件或系统

发表于 08-10 06:25

如何在Arduino中使用20x4 I2C字符LCD显示器

电子发烧友网站提供《如何在Arduino中使用20x4 I2C字符LCD显示器.zip》资料免费下载

发表于 06-28 15:57

•0次下载

请问DSP和FPGA的时钟信号如何产生?

我做的一个基于DSP的系统中,DSP做主处理器,控制着整个系统,包括信号处理,整体调度等;选择了一块Xilinx的FPGA做FIFO UART和系统

发表于 06-19 06:43

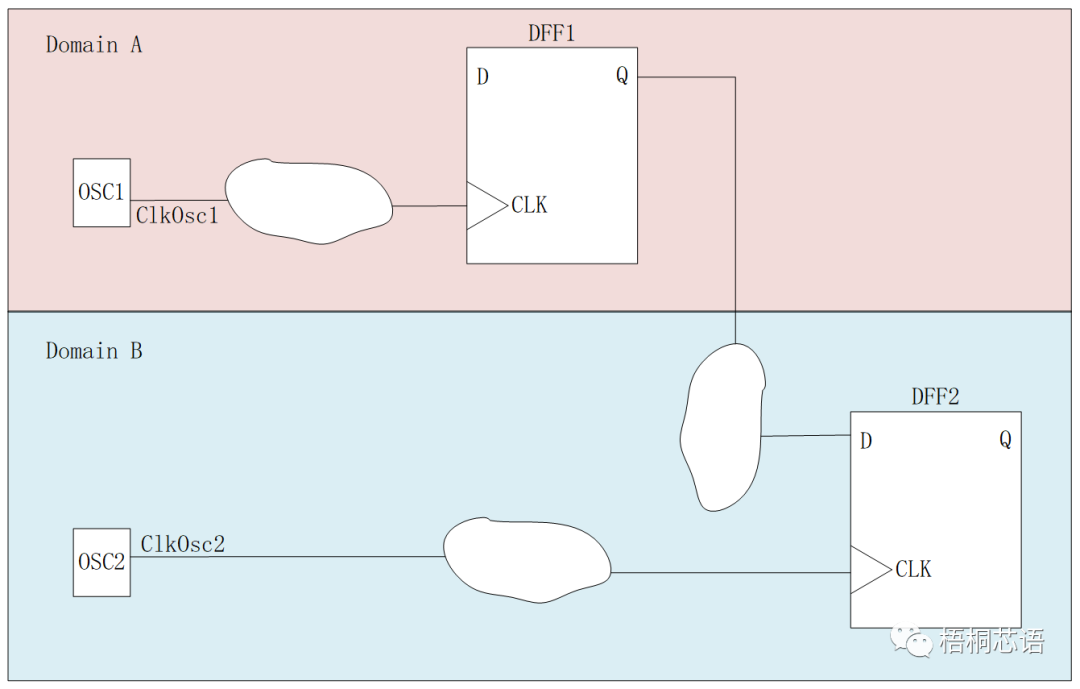

高级FPGA设计技巧!多时钟域和异步信号处理解决方案

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率

发表于 06-02 14:26

如何在linux应用程序中使用pwm捕获?

/402e4000.pwm/pwm/pwmchip6/pwm0# cat capture

cat: capture: 函数未实现

那么,如何在 linux 应用程序中使用 pwm 捕获?

发表于 05-10 07:05

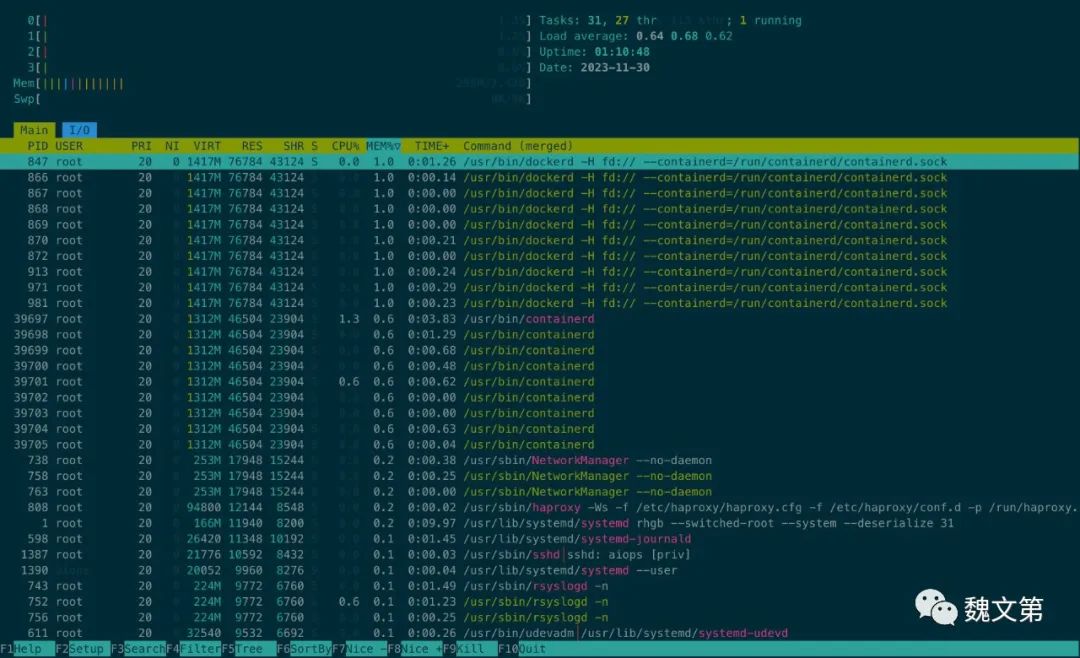

如何在System Generator中使用多个时钟域实现复杂的DSP系统

如何在System Generator中使用多个时钟域实现复杂的DSP系统

评论