声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

内核

+关注

关注

3文章

1309浏览量

39825 -

赛灵思

+关注

关注

32文章

1794浏览量

130489 -

同步

+关注

关注

0文章

89浏览量

19007

发布评论请先 登录

相关推荐

Xilinx LogiCORE IP视频定时控制器内核简介

Xilinx LogiCORE IP视频定时控制器内核是一款通用视频定时生成器和检测器。该内核可通过完整的寄存器集进行高度编程,从而控制各种定时生成参数。这种可编程性与一组全面的中断位

LogiCORE IP JESD204内核概述

LogiCORE IP JESD204内核实现了一个JESD204B接口,使用GTX、GTH、GTP或GTY(仅限UltraScale和UltraScale+)收发器在1至8个通道上支持1至12.5

LogiCORE IP AXI4-Stream FIFO内核解决方案

LogiCORE IP AXI4-Stream FIFO内核允许以内存映射方式访问一个AXI4-Stream接口。该内核可用于与AXI4-Stream IP接口,类似于LogiCORE

XILINX FPGA IP之FIFO Generator例化仿真

上文XILINX FPGA IP之FIFO对XILINX FIFO Generator IP的特性和内部处理流程进行了简要的说明,本文通过实际例子对该

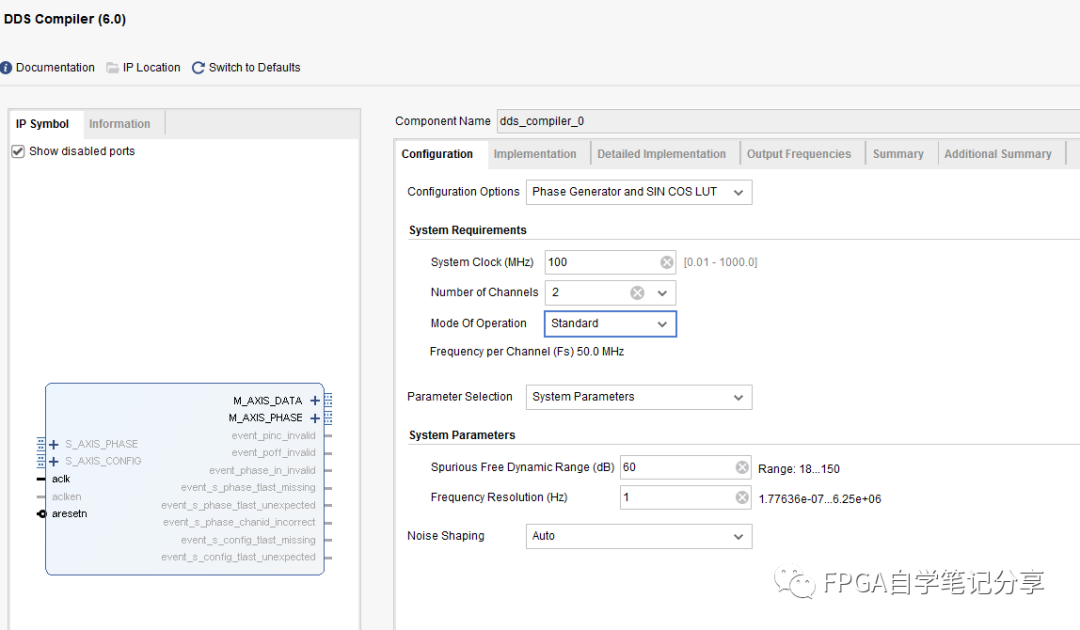

XILINX FPGA IP之DDS Compiler_ip例化仿真

之前的文章对dds ip 的结构、精度、参数、接口进行了详细的说明,本文通过例化仿真对该IP的实际使用进行演示。本文例化固定模式和可配置模式两种模式分别例化ip并仿真,说明该

Xilinx Vivado DDS IP使用方法

DDS(Direct Digital Frequency Synthesizer) 直接数字频率合成器,本文主要介绍如何调用Xilinx的DDS IP核生成某一频率的Sin和Cos信号。

从Xilinx FFT IP核到FPGA实现OFDM

笔者在校的科研任务,需要用FPGA搭建OFDM通信系统,而OFDM的核心即是IFFT和FFT运算,因此本文通过Xilinx FFT IP核的使用总结给大家开个头,详细内容可查看官方文档PG109。

XILINX FPGA IP之MMCM PLL DRP时钟动态重配详解

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

发表于 06-12 18:24

•6070次阅读

XILINX FPGA IP之Clocking Wizard详解

锁相环基本上是每一个fpga工程必不可少的模块,之前文档xilinx 7 系列FPGA时钟资源对xilinx fpga的底层时钟资源做过说明,但是对于fpga的应用来说,使用Clocking Wizard IP时十分方便的。

发表于 06-12 17:42

•3117次阅读

eBPF,何以称得上是革命性的内核技术?

eBPF 的全称是 extended Berkeley Packet Filter,它被称之为 “革命性” 的内核技术,可以在 Linux 内核中运行沙盒程序,而无需更改内核源代码或加载内核

Xilinx ST 2059 IP内核技术的演示

Xilinx ST 2059 IP内核技术的演示

评论