声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

编码器

+关注

关注

41文章

3355浏览量

131421 -

赛灵思

+关注

关注

32文章

1794浏览量

130497 -

HEVC

+关注

关注

1文章

36浏览量

23809

发布评论请先 登录

相关推荐

编码器安装对电机测速的影响?

,但是编码器绝对没有打滑。

请问这个编码器是否同心对电机测速影响这么大吗?我的理解电机转一圈编码器转一圈,只要转动的每一圈距离时长一样应该是没有问题的,但是在变频

发表于 03-06 17:34

伺服电机编码器故障及维修 伺服电机编码器调零对位方法

伺服电机的编码器是用来测量电机转动角度和速度的重要部件。然而,由于长时间运行、环境因素等原因,编码器可能会出现故障,影响电机的准确运行。下面将介绍伺服电机

编码器好坏怎么判断,编码器原理

编码器(Encoder)是将输入数据转化为特定编码表示的一种技术。对于不同类型的编码器,评判其好坏可以从多个方面进行考量,包括编码质量、速度、模型结构等。

磁性编码器和光电编码器的比较

伺服电机编码器是一种关键的反馈装置,用于测量和控制电机的转速和位置。在选择伺服电机编码器时,常常面临一个选择:使用磁电编码器还是光电编码器。接下来将从几个关键方面比较这两种类型的

6RA70系统在直流电机编码器坏时,如何摔掉编码器继续运行?

有两个直流电机,各自有自己的编码器,脉冲编码器(1024),此两个电机在运行时要同时进行调速,并保证速度一致,各自的速度给定,通过按钮给定的,按一下增加10HZ,最大为50HZ,如果其中一台编

发表于 01-01 08:12

AD9467输出电平标准为LVDS,是否支持连接FPGA BANK1.8V?

我已经看过AD9467的评估板在ZEDboard和KC705的引脚约束为\"LVDS_25\",对应FPGA的BANK VCCO供电2.5V,但是现在我的项目中FPGA BANK 的VCCO供电是1.8V,我对其做引脚约束为\"

发表于 12-11 06:36

使用KC705板上晶振作为参考时钟生成DCI和data,有很多跳动的杂波信号是怎么回事?

最近配置AD9139的时候,分别采用了两种方式。一种是直接使用KC705板上晶振作为参考时钟生成DCI和data,DAC单独供参考时钟,另一种是使用AD9139评估板分频得到的DCO作为FPGA

发表于 12-04 06:53

STM32 Encoder编码器使用总结

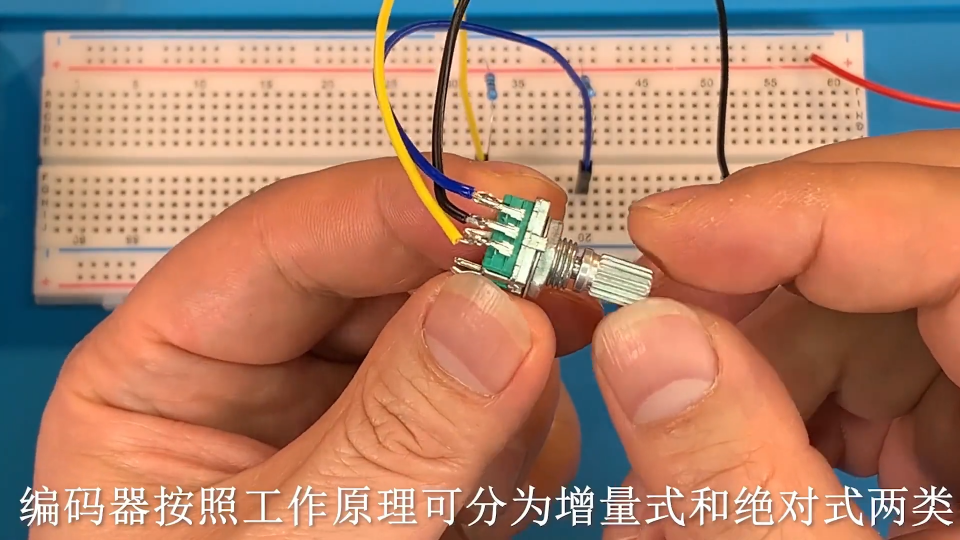

的Encoder接口的电机运行,相应的仿真和实验都是基于一个1024脉冲的增量式光电编码器,关于模型的建模也是基于实际的实验电机和实际的编码器。Encoder 原理实物图如下,2500P/R就是电机机械转36

发表于 05-06 09:44

•2次下载

在KC705 Kintex-7评估平台上运行的HEVC编码器的演示

在KC705 Kintex-7评估平台上运行的HEVC编码器的演示

评论