声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

赛灵思

+关注

关注

32文章

1794浏览量

130491 -

调试

+关注

关注

7文章

527浏览量

33621 -

设计

+关注

关注

4文章

814浏览量

69698

发布评论请先 登录

相关推荐

如何禁止vivado自动生成 bufg

在Vivado中禁止自动生成BUFG(Buffered Clock Gate)可以通过以下步骤实现。 首先,让我们简要了解一下什么是BUFG。BUFG是一个时钟缓冲器,用于缓冲输入时钟信号,使其更稳

Vivado Design Suite 用户指南:编程和调试

《Vivado Design Suite 用户指南:编程和调试》 文档涵盖了以下设计进程: 硬件、IP 和平台开发 : 为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 AMD

vivado使用误区与进阶资料

Applications”,其实也是专为 Vivado 而设的一个部门,从 Vivado 的早期计划开始,我和我的同事们就投入到了 Xilinx©和Vivado 的客户们的推广和支持中

发表于 09-20 06:31

Vivado Design Suite用户指南:编程和调试

电子发烧友网站提供《Vivado Design Suite用户指南:编程和调试.pdf》资料免费下载

发表于 09-13 14:47

•0次下载

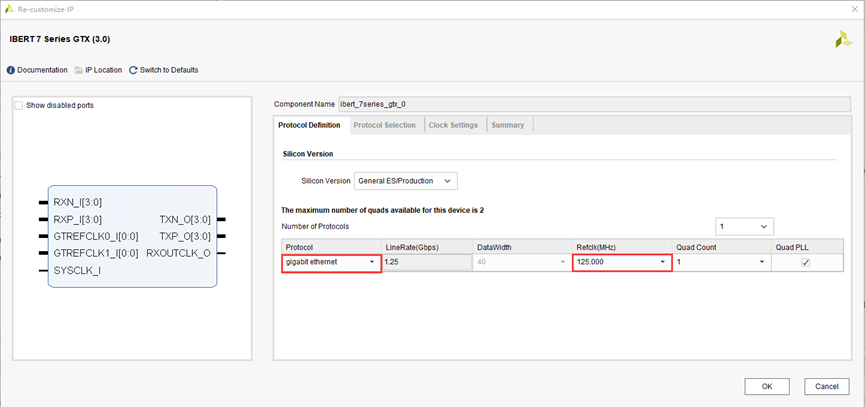

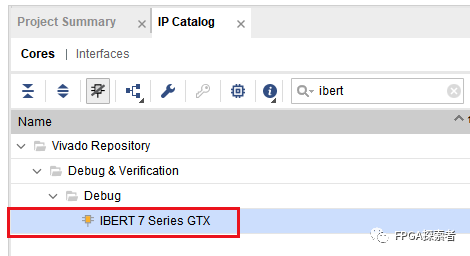

基于IBERT的GTX数据传输测试

本文介绍一个FPGA开源项目:基于IBERT的GTX数据传输测试。IBERT是指误码率测试,在Vivado软件中,IBERT 7 Series GTX IP核可用于对 Xilinx F

安全光幕的调试步骤

安全光幕的调试步骤 很多机械设备在安装好安全光幕之后,都需要进行安全光幕的调试工作,以防止设备及安全光幕在正式运行时出现问题。那么安装安全光幕之后的调试工作应该怎样进行呢? 1:检测指

Versal GTM如何用Tcl命令在IBERT生成QPRBS13序列

目前对于 Vivado 2023.1 版本的 IBERT GUI 界面暂时不支持 QPRBS13 的设置,需要通过 tcl 或者端口设置的方法来实现。

ZC706评估板IBERT误码率测试和眼图扫描

IBERT(Integrated Bit ErrorRatio Tester,集成误比特率测试工具),是Xilinx提供用于调试FPGA高速串行接口比特误码率性能的工具,最常用在GT高速串行收发器测试

利用IBERT核对GTX收发器板级测试

上的Tx和Rx接口互相连接,其中一个通道上的模式设置为Far_End_PMA或Far_End_PCS模式,另一个通道设置为默认的None模式并监测误码率。

Vivado中IBERT默认模式为None模式

发表于 06-21 11:23

Xilinx FPGA远程调试方法(二)

上篇主要是分享了Vivado编译软件远程调试的方法。杰克使用Vivado软件进行远程连接,主要是用于固化程序以及FPGA(PL端)的异常排查。而本篇主要内容是对使用Vitis软件远程调试

发表于 05-25 14:36

•1766次阅读

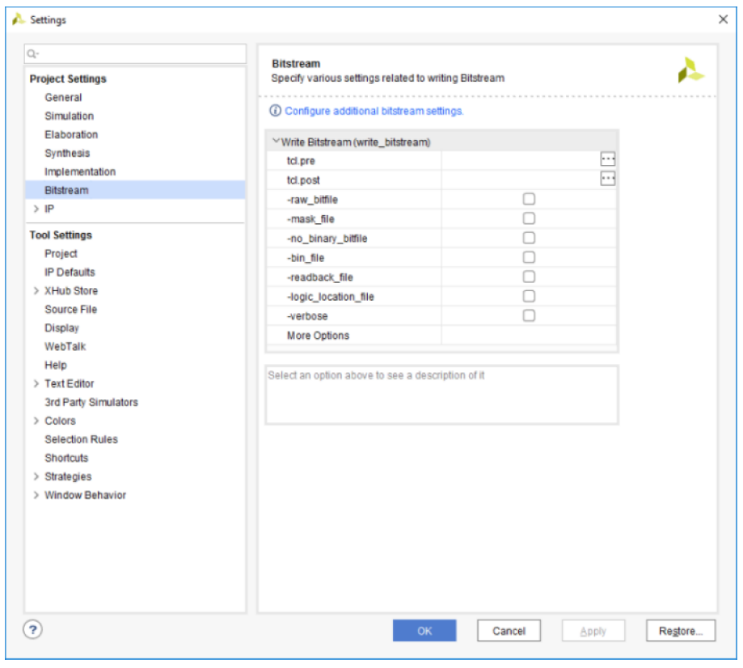

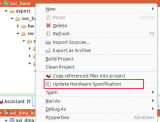

使用Vivado 2016.3中IBERT调试的好处及步骤

使用Vivado 2016.3中IBERT调试的好处及步骤

评论