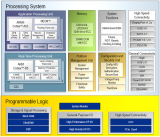

ZYNQ系列是赛灵思公司(Xinlinx)推出的行业第一个可扩展处理平台,旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。该系列四款新型器件得到了工具和IP提供商等生态系统的支持,将完整的 ARM® Cortex™-A9 MPCore 处理器片上系统 (SoC)与 28nm 低功耗可编程逻辑紧密集成在一起,可以帮助系统架构师与嵌入式软件开发人员扩展、定制、优化系统,并实现系统级的差异化。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

处理器

+关注

关注

68文章

18250浏览量

222075 -

嵌入式

+关注

关注

4981文章

18271浏览量

288316 -

赛灵思

+关注

关注

32文章

1794浏览量

130510

发布评论请先 登录

相关推荐

使用 PCIE 更新 AMD ZYNQ™ 的 QSPI Flash 参考设计

/r/en-US/ug585-zynq-7000-SoC-TRM

环境需求

硬件环境:

ZC706 开发板

Windows10/11 或者 Ubuntu20.04 主机

软件环境:

Vivado

发表于 11-30 18:49

ZYNQ常用外设设计 (上)

Step3: 按照“Vivado中进行ZYNQ硬件部分设计”中介绍的,直到在SDK中编写C代码步骤。需要使用UART进行通行,分为通过UART向外发送数据和通过UART接收数据。

Zynq UltraScale+ MPSoC软件开发人员指南

电子发烧友网站提供《Zynq UltraScale+ MPSoC软件开发人员指南.pdf》资料免费下载

发表于 09-15 10:16

•8次下载

Zynq UltraScale+ MPSoC:软件开发者指南

电子发烧友网站提供《Zynq UltraScale+ MPSoC:软件开发者指南.pdf》资料免费下载

发表于 09-14 10:03

•10次下载

使用Zynq平台进行嵌入式软件和FPGA设计时有哪些挑战

本文介绍了在AMD Xilinx Zynq平台上实现嵌入式软件和FPGA设计的集成工作流程,使用Simulink进行Zynq模型设计,以及使用HDL协同仿真和FPGA-in-Loop进

xilinx ZYNQ7000系列基本开发流程之PS端

ZYNQ 芯片分为 PL 和 PS, PS 端的 IO 分配相对是固定的,不能任意分配,虽然 PS 端的 ARM 是硬核,但是在 ZYNQ 当中也要将 ARM 硬核添加到工程当中才能使用,FPGA

ZYNQ(FPGA)与DSP之间GPIO通信实现

本文主要介绍说明XQ6657Z35-EVM 高速数据处理评估板ZYNQ(FPGA)与DSP之间GPIO通信的功能、使用步骤以及各个例程的运行效果。1.1 ZYNQ与DSP之间GPIO通信1.1.1

发表于 06-16 16:02

Zynq软件的基本介绍

Zynq软件的基本介绍

评论