Clock Uncertainty跟图1所示的几个因素有关。当时序违例路径的Clock Uncertainty超过0.1ns时,应引起关注。这一数值可在时序报告中查找到,如图2所示,如果需要降低Clock Uncertainty,可采用如图3所示的流程。

图1 Clock Uncertainty相关因素

图2 Timing Report中查看Clock Uncertainty

图3 降低Clock Uncertainty的操作流程

01

同步时钟是否由两个并行的MMCM或PLL生成

在UltraScale和UltraScale Plus系列芯片中,BUFGCE_DIV可提供分频功能。如图4所示,如果需要通过MMCM生成两个时钟,其频率分别为300MHz和600MHz。此时,可利用BUFGCE_DIV的分频功能,同时可对这两个时钟设置CLOCK_DELAY_GROUP属性,从而降低Clock Uncertainty。

图4 利用BUFGCE_DIV生成分频时钟

02

生成时钟其Discrete Jitter>0.05ns?

Discrete Jitter是由MMCM/PLL引入的,其具体数值可通过点击图2中Clock Uncertainty的数值查看,如图5所示。通常,VCO的频率越高,引入的DiscreteJitter会越小。因此,可通过手工调整VCO的频率(在ClockingWizard中修改M和D两个参数)达到降低Discrete Jitter的目的。此外,如果可以的话,用PLL替代MMCM。相比于MMCM,PLL引入的Jitter会小一些。

图5 查看Discrete Jitter具体数值

03

同步跨时钟域路径是否超过1000条

过多的同步跨时钟域路径会对时序收敛带来一定的挑战,尤其是时钟频率比较高时,例如频率为500MHz。此时要检查这些路径。

(1)能否对这些路径设置多周期路径约束

(2)在Latency允许的情况下,通过FIFO或XPM_CDC处理跨时钟域路径

-

时钟

+关注

关注

10文章

1479浏览量

130302

原文标题:深度解析ug1292(9)

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA里面关于时序约束的问题。。求大神指导

SysBios clock的问题

FPGA报错,添加了时钟时序,还有这个报错怎么解决?

FPGA报错,添加了时钟时序怎么解决?

Agilent Uncertainty Analysis B

Determining Clock Accuracy Req

芯片设计之逻辑综合过程(下)

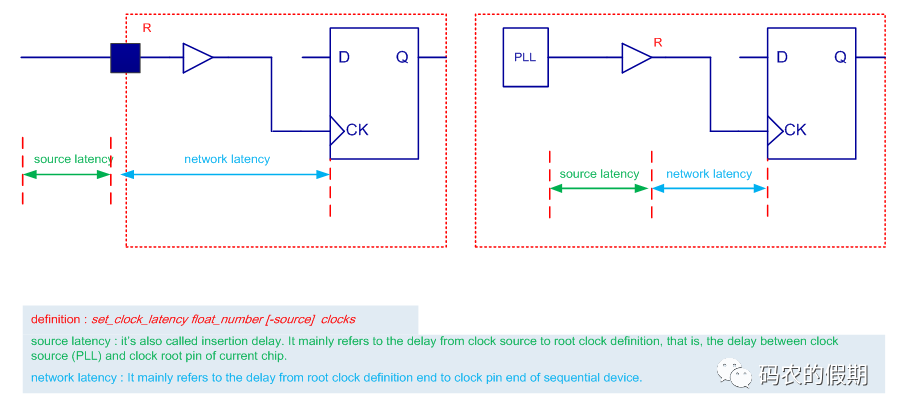

探讨下clock的基本定义(上)

探讨下clock的基本定义(下)

降低Clock Uncertainty流程

降低Clock Uncertainty流程

评论