三态缓冲器工作原理

三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,其三态输出受到使能输出端的控制,当使能输出有效时,器件实现正常逻辑状态输出(逻辑0、逻辑1),当使能输入无效时,输出处于高阻状态,即等效于与所连的电路断开。

缓冲器是数字元件的其中一种,它对输入值不执行任何运算,其输出值和输入值一样,但它在计算机的设计中有着重要作用。

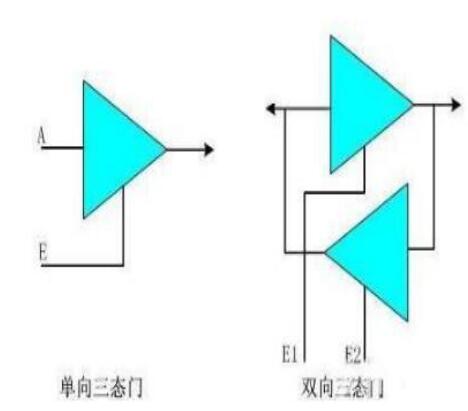

缓冲器分为两种,常用缓冲器(常规缓冲器)和三态缓冲器。常规缓冲器总是将值直接输出,用于将电流输出到高一级电路系统。三态缓冲器除了常规缓冲器的功能外,还有一个选项卡通输入端,用E表示。当E=0和E=1时有不同的输出值。

缓冲器又可以分为输入缓冲器和输出缓冲器两种。前者的作用是将外设送来的数据暂时存放,以便处理器将它取走;后者的作用是用来暂时存放处理器送往外设的数据。有了数控缓冲器,就可以使高速工作的CPU与慢速工作的外设起协调和缓冲作用,实现数据传送的同步。由于缓冲器接在数据总线上,故必须具有三态输出功能。

当E=1时,选通,其输入直接送到输出;

若E=0,缓冲器被阻止,无论输入什么值,输出的总是高阻态,用Z表示。高阻态能使电流降到足够低,以致于类似缓冲器的输出没有与任何东东相连。

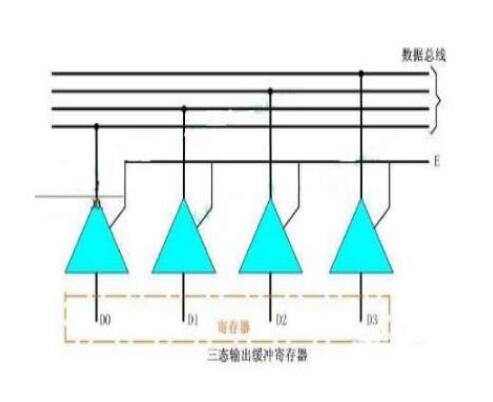

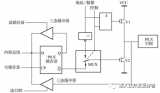

为减少信息传输线的数目,大多数计算机中的信息传输线均采用总线形式,即凡要传输的同类信息都走同一组传输线,且信息是分时传送的。在计算机中一般有三组总线,即数据总线、地址总线和控制总线。为防止信息相互干扰,要求凡挂在总线上的寄存器或存储器等,它的传输端不仅能呈现0、1两个信息状态,而且还应能呈现第三种状态——高阻抗状态(又称高阻状态),即此时好像它们的输出被断开,对总线状态不起作用,此时总线可由其它器件占用。即可实现上述的功能,它除具有输入输出端之外,还有一控制端,请看下图。

当控制端E=1时,输出=输入,此时总线由该器件驱动,总线上的数据由输入数据决定;

当控制端E=0时,输出端呈高阻抗状态,该器件对总线不起作用。当寄存器输出端接至三态门,再由三态门输出端与总线连接起来,就构成三态输出的级冲寄存器。如下图所示就是一个4位的三态输出缓冲寄存器。由于这里采用的是单向三态门,所以数据只能从寄存器输出到数据总线。如果要实现双向传送,则要用双向三态门。

-

缓冲器

+关注

关注

6文章

1566浏览量

44870 -

三态缓冲器

+关注

关注

1文章

6浏览量

4359

发布评论请先 登录

相关推荐

XC7SH125总线缓冲器/线路驱动器;三态产品数据表资料

AD9280三态引脚是否只是控制数据输出端的,和转换过程没有关系?

请问如何将缓冲器与AD8221搭配使用 ?

51端口的结构及工作原理介绍

如何设计和使用缓冲器

三态输出的缓冲器有哪些用途?

Versal HDIO OBUFT和IOBUF三态时序影响

MAX13256的缓冲器设计

8051单片机基本操作

三态缓冲器工作原理

三态缓冲器工作原理

评论