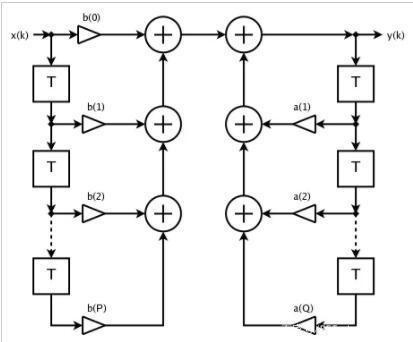

1、高斯滤波器的实现方式

方法1:与高斯核直接进行卷积实现,这样使用的资源和乘法器 加法器都会很多。例如3*3窗口的滤波核进行卷积运算,一共需要进行9次乘法和8次加法。

方法2:采用两个一维的高斯滤波进行两次滤波,即先对行进行一维滤波,然后再对列进行一维滤波,这样计算简单,降低了复杂度。

比较两种方法,采用第二种实现方法。

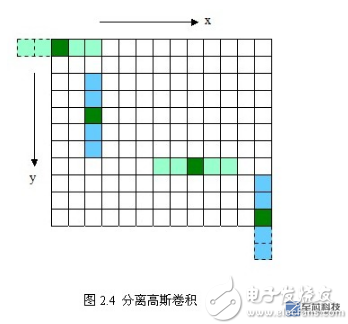

2、行列分离计算方法

采用下图的计算方法,其中对边界的处理填0处理。

3、实现结果

always

begin

#10 clk = ~clk; //100Mhz

end

时间:5201520000ps=5.2ms

always

begin

#5 clk = ~clk; //200Mhz

end

时间:2600780000ps=2.6ms

4、与仿真比较

如下图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1600文章

21281浏览量

592853

发布评论请先 登录

相关推荐

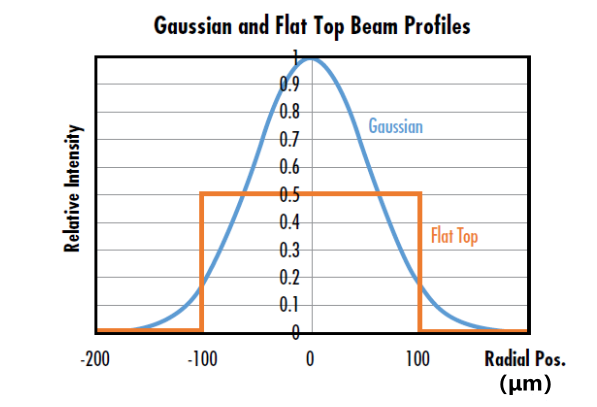

什么是高斯光束

图1:高斯光束和平顶光束在相同的光功率下,显示高斯光束的峰值强度是平顶光束的两倍 大多数激光束都是高斯光束,尽管在某些情况下,具有非高斯辐照度分布是有益的。随着离激光束横截面中心的距离

基于多速率DA的根升余弦滤波器的FPGA实现

Add Cell,MAC)结构,设计方便,只需要乘法器、加法器和移位寄存器即可实现,但是在FPGA中实现硬件乘法器十分耗费资源。特别是当滤波器阶数很高时,资源耗费不可忽视。若采用乘法

发表于 03-25 14:21

详解从均值滤波到非局部均值滤波算法的原理及实现方式

将再啰嗦一次,详解从均值滤波到非局部均值滤波算法的原理及实现方式。 细数主要的2D降噪算法,如下图所示,从最基本的均值滤波到相对最好的BM3D降噪,本文将尽量用最同属的语言,详解这些算

基于FPGA图像处理的高斯模糊实现

高斯模糊(Gaussian Blur)是一种高斯低通滤波,可以过滤掉图像的高频部分,保留低频部分,对于去除高斯噪声非常有效果,常常被用于图像去噪中。

发表于 10-26 09:36

•310次阅读

Lake Shore410高斯计介绍

。大多数的操作功能都可以通过按前面板的一或两个键来实现。410高斯计可以用高斯(G)和特斯拉(T)两种单位来显示磁场;对直流或交流磁场都可以进行测量,磁场的*小分辨率为0.1G;主要功能包括峰值锁定

发表于 06-15 11:07

模拟无源滤波器设计(九)-Gaussian滤波器设计详解

文章详细对高斯滤波器的综合设计进行讲解,解释如何从时域无过冲推导出高斯滤波器的。并且深入探讨了高斯滤波

FPGA 实现线性相位 FIR 滤波器的注意事项

点击上方 蓝字 关注我们 本文将回顾对称 F IR 滤波器 的高效 FPGA 实现的注意事项。 本文将推导对称 FIR 滤波器的模块化流水线结构。我们将看到派生结构可以使用 Xi

关于高斯滤波器的响应和逼近

本文讨论了一种滤波器,其幅频响应特性为,其中是频率的函数,是与滤波器带宽相关的常数。该滤波器的幅度响应曲线具有高斯概率函数的形状,结果表明,相位响应曲线基本上是线性的。以前的研究人员已

FPGA 实现 高斯滤波

FPGA 实现 高斯滤波

评论