在电子设备和通信系统的设计和布局中,必须仔细考虑晶体振荡器和外围电路,以优化性能。作为信号源的核心,晶体振荡器必须产生很高的精度输出,因此对高频率噪声从其他的板上来说是非常敏感的。

这种电路在设计时需要明确的注意。这些技术说明是在一些外围电路中减少噪音的设计指南,在这些电路中高频噪声对晶体振荡器的输出尤其有利。

噪声来源

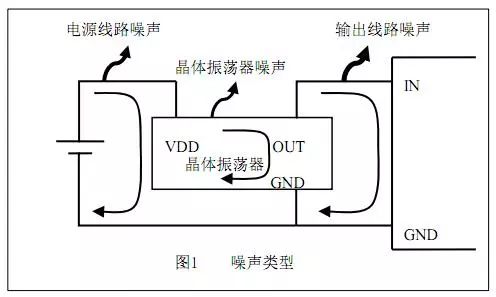

首先,在图1中,我们指出了典型的由晶体振荡器和外围电路产生的噪声。

有三个主要的噪声源:

1.电源线路噪声

2.输出线路噪声

3.晶体振荡器的噪声

通常被称为“噪声”的是这三个因素的累积结果。

下面我们将对地址类型的噪声进行解释。

1、电源线路噪声

电压波纹和开关噪声通常是由电源线发出的。这种噪声会影响晶体振荡器的输出。此外,有必要确保晶体振荡器产生的波纹噪声不会流到电源线上。实施这些措施还可以改善隔离,防止其他设备产生的外部噪声流入晶体振荡器,从而保证晶体振荡器的稳定性。

2、输出线路噪声

输出线噪声是指输出线作为天线的晶体振荡器输出的信号。对于输出信号和物理跟踪,应该实现降低噪声的技术。

3、晶体振荡器噪声

晶体振荡器的噪音是指晶体振荡器内部集成电路和电路发出的噪声。要解决这一噪声,需要确保晶体振荡器稳定的电源供应,并确保所需波形的形成,以实现晶体振荡器的稳定运行。

这些噪声源依赖于上述的原因,并可通过本文稍后所提到的功率线和输出线技术间接地减轻。

上述电源发出的噪声水平与电流和电流环路径成正比。因此,电流或电流回路阻抗的降低会导致发射噪音的降低。一般来说,电流和电流环路径长度与晶体振荡器及其外围电路有关。

电流量: 电源线=晶体振荡器>输出线

电流环大小: 输出线>电源线>晶体振荡器

输出线噪声对晶体振荡电路有最大的影响,其次是功率线的噪声贡献。实际晶体振荡器所发出的噪声比其他两种来源的噪声要低得多。

噪音对策

在这些技术说明中,我们已经研究了晶体振荡器及其外围电路中的噪声来源。在这里,我们解释减少噪音的措施。主要有三种降噪措施:

1.建立稳定的电源和接地连接。

2.安装滤波器以防止电源线产生噪声。

3.在主板上配置一条稳定的输出线。

1、稳定的电源和接地连接

稳定的电源和接地是指在宽频带(特别是高频率)的极低的阻抗水平,以及在带宽的所有点上达到均匀电势的导体。特别是,接地线代表电路的基本电势,因此必须达到最大的稳定水平。这就需要设计一种具有不收缩的宽表面积的接地平面。

在多层板上,额外的接地平面用来在独立层上配置电源线和地线。当设计涉及焊点,更广泛的接触面积确保更低的阻抗,因此更少的噪音。

2、电源线滤波器

通常,在电源线和地线之间放置一个滤波器,以防止晶体振荡器的噪音泄漏到电源或接地线,反之亦然,以防止电源线的噪音进入晶体振荡器。通常,旁路电容器用作电源线和地线的滤波器。下面提供详细的解释。

A.旁路电容

旁路电容器可以降低相互作用的阻抗,并帮助稳定电路的工作,同时吸收电力线上存在的噪声。这是一种众所周知的消噪方法。用适当的电容值安装电容器将解决大部分与噪音有关的问题。

I、旁路电容容量值

标准旁路电容值在0.01μF和1μF之间。该值应尽可能低,但在电源端子VCC和电源线阻抗相对于地面的频率范围内是晶振频率的三倍。在这里,您必须确认此频率的频率特性,以确保高频侧或低带侧的阻抗电平不增加。

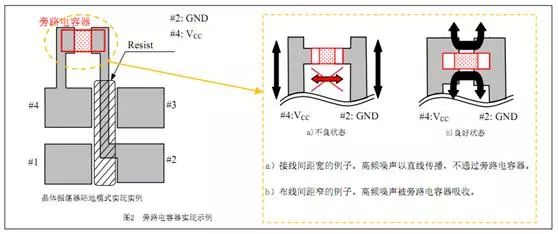

II、安装旁路电容器

为了减小噪声,旁路电容应尽可能靠近晶体振荡器安装。随着跟踪长度的增加,寄生电感将增加,并导致更高频率的阻抗增加。旁路电容的跟踪长度应配置,以便信号通过连接到电源线。这将迫使噪声通过旁路电容器,并改善噪声消除效果。

避免在图2a中显示的类型。安装旁路电容器时。高频噪声通常以直线的方式传播,所以如果采用如图2a所示的模式,噪声就不会通过旁路电容器。因此,使用图2b中所示的模式。

III、配置稳定的输出行

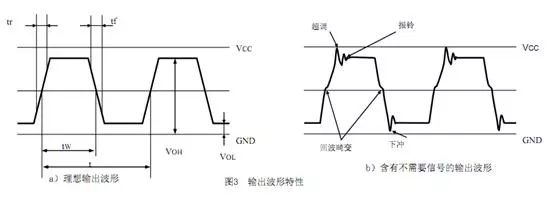

稳定的输出线是指能够有效地将晶体振荡器的输出波形转换为所需输入的信号,并且具有最小的失真和电磁辐射。配置稳定输出线的关键在于确保输入所需的波形属性,如tr、tf、VOH、VOL等。

此外,稳定的输出线需要消除不必要的信号,如超调、低射、振铃和回声,如图3b所示。为了减少不必要的辐射,了解跟踪的天线效率也是很重要的。

防止输出波形失真的措施包括:

a.配置串行电阻

b.配置终端电阻

c.配置过滤器

d.匹配输出线阻抗

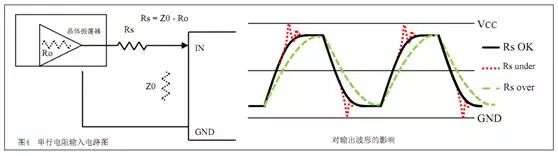

a.配置串行电阻

连接一个晶体振荡器输入设备通常在波形失真,包括过冲,下冲和振铃的生产结果。这些扭曲的高频成分,3-7倍的振荡频率和产生噪声,应取消发射。

为了消除这种失真,串行电阻连接在晶体振荡器的输出端和输出线之间,如图4所示。电阻值可以使晶体振荡器的输出阻抗的总和(RO)和串联电阻(RS)相当于输出线路阻抗(Z0)。

可以进行测试,以确定串行电阻的最佳值。测试方法包括用示波器测量输出波形,并从低到高的值进行串联电阻的转换。最优阻值是指超冲、低射和振铃的值都被消除了。

b.配置终端电阻

终端电阻的配置在很大程度上取决于接口的类型和使用的时钟线的类型。配置将根据这些因素而变化。

一般来说,当输出线上的阻抗与设备输入的阻抗不匹配时,输出波形会发生失真。当阻抗不匹配时,行波不能完全接收,部分信号被反射回振荡器,从而导致输出波形失真。这导致高频噪声。

当分支晶体振荡器输出到多个设备时,这种波形失真会导致触发错误。因此,正确的终止和阻抗匹配是至关重要的。

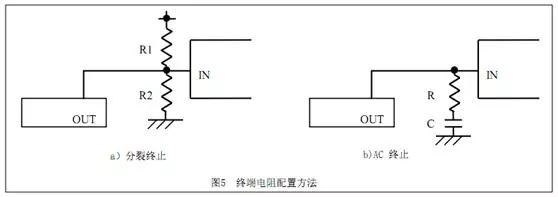

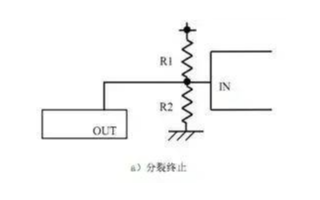

为了防止来自接收设备的回声,输入端应与输出线上的阻抗值相同。图5显示了两种常见的终止方法:分裂终止和AC终止。

c.配置过滤器

通常,输出波形失真可以通过串行电阻或终端电阻来解决。在这些方法不能解决问题的情况下使用过滤。滤波器的使用是消除高频噪声的一种有效方法,但这种方法会导致TR和TF(波形耗散)的增加。

因此,您必须选择一个适合TR和TF属性的过滤器。另外,使用更大的电容器作为滤波器可以导致电流的增加,反之则会导致噪声的增加。

d.输出线阻抗匹配

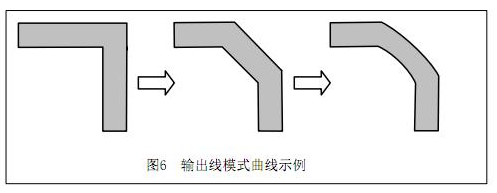

减少输出线上的波形回波要求输出线阻抗尽可能一致。如图6所示,实现一致的输出线路阻抗涉及到输出线模式曲线配置使直角转变成45º角或,如果可能的话,一个圆形的曲线。另外,避免使用通孔或T形。

最后,我们将介绍两种最重要的减少噪音排放的方法。

a.使用更短的输出线

在所有电路中,输出线最容易产生噪声。因此,在设计和布局时,应优先考虑允许最短输出线不出现阻抗波动。使用较短的布线将输出线谐振频率移到高频侧。频率越高,输出频率元件就会产生更多的阻尼,从而导致噪声的降低。

b.使用较短的电流环路径

如上所述,输出线发出的噪声电平与当前环路路径长度成比例。因此,重要的是,晶体振荡器和输入设备的输出和接地轨迹应尽可能短。实现这一点的一个简单方法是将接地平面安装在输出跟踪的对侧。

如以上所述,对晶体振荡器及其外围电路进行仔细的电路设计是降低噪声的关键。最佳电路设计可以避免与噪声有关的问题,并使设备能够充分发挥其性能潜力。

-

电路

+关注

关注

170文章

5477浏览量

169376 -

振荡器

+关注

关注

28文章

3507浏览量

137607 -

噪声

+关注

关注

13文章

1070浏览量

47055

原文标题:史上最全!电路降噪指南,告诉你一个正确学习姿势

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

分享一些嵌入式系统编程中内存操作相关的避坑指南

电源纹波噪音测试中需要注意的一些问题总结

关于stm32的一些简单的介绍

用中位过滤器执行简单的ADC取样减少噪音

设计外围电路时如何减少噪音

一些外围电路中减少噪音的设计指南

一些外围电路中减少噪音的设计指南

评论