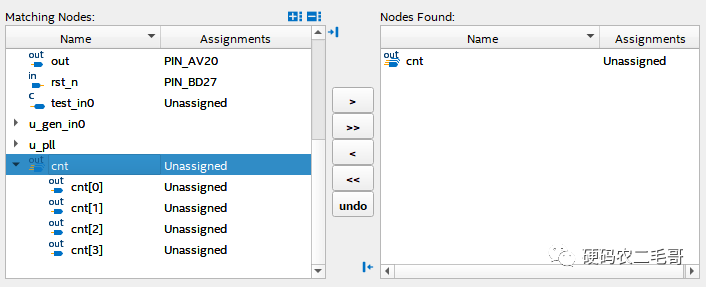

1、 信号前面将keep hierarchy选择YES ,或者选择soft(在综合时保持层次),这样有利于你从模块中找到你想抓取的信号和信号名不被更改。

2、 信号前面使用 (* KEEP = “{TRUE|FALSE |SOFT}” *),可以防止信号被综合掉,但是无法防止在布局布线的时候优化掉。

3、 信号前面使用(* DONT_TOUCH= “{TRUE|FALSE}” *),可以防止信号在综合,以及布局布线的时候被优化掉。

注意: 右边的TRUE|FALSE必须要大写,否则会报错,无法识别TRUE|FALSE为1|0.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1599文章

21273浏览量

592820

发布评论请先 登录

相关推荐

是否有更好的方法可以防止ADC被烧坏?

的方法可以防止ADC被烧坏

如果减法电路处的AD4622使用单电源工作,根据手册显示,正负输入最低电压耐受-0.3V,应该会被击穿,有什么办法可以在单电源供电下让这个减法电路在输出为负时防止

发表于 01-15 06:02

pwm产生的三种方法

技术被广泛应用于电力电子器件(如IGBT、MOS)的控制中,也可以用于调节LED照明、伺服电机等应用中。本文将详细介绍PWM产生的三种方法。 一、比较式PWM 比较式PWM是最常见的PWM产生方法,它通过比较一个变量信号与一个固

Vivado综合阶段什么约束生效?

Vivado综合默认是timing driven模式,除了IO管脚等物理约束,建议添加必要的时序约束,有利于综合逻辑的优化,同时综合后的design里面可以评估时序。

【世说设计】噪声系数测量的三种方法

本文介绍了测量噪声系数的三种方法:增益法、Y系数法和噪声系数测试仪法。这三种方法的比较以表格的形式给出。在无线通信系统中,噪声系数(NF)或者相对应的噪声因数(F)定义了噪声性能和对接

今日说“法”:如何防止reg、wire型信号在使用逻辑分析仪时被优化

于wire和reg型信号类型。

2、使用Synplify Pro综合

使用Synplify Pro综合时防止信号

发表于 05-16 17:48

Vivado综合参数设置

如果你正在使用Vivado开发套件进行设计,你会发现综合设置中提供了许多综合选项。这些选项对综合结果有着潜在的影响,而且能够提升设计效率。为了更好地利用这些资源,需要仔细研究每一个选项

Vivado防止信号被综合掉的三种方法

Vivado防止信号被综合掉的三种方法

评论