集成电路按晶体管的性质分为TTL和CMOS两大类,TTL以速度见长,CMOS以功耗低而著称,其中CMOS电路以其优良的特性成为目前应用最广泛的集成电路。

有初学者在使用CMOS集成电路时,有些多余的输入端,做悬空处理,是非常不当的做法。

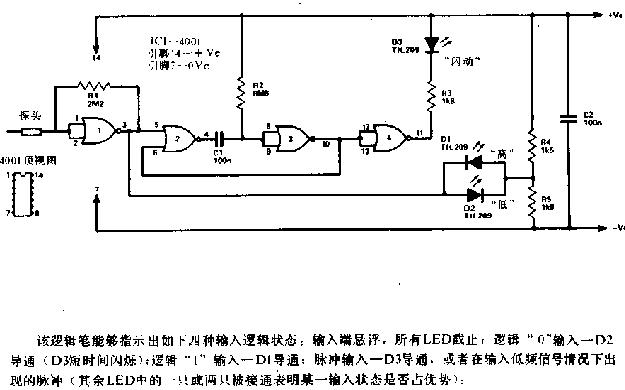

CMOS电路的输入端是不允许悬空的,因为悬空会使电位不定,破坏正常的逻辑关系。另外,悬空时输入阻抗高,易受外界噪声干扰,使电路产生误动作,而且也极易造成栅极感应静电而击穿。所以“与”门,“与非”门的多余输入端要接高电平,“或”门和“或非”门的多余输入端要接低电平。若电路的工作速度不高,功耗也不需特别考虑时,则可以将多余输入端与使用端并联。

除了以上这一点,关于CMOS集成电路的使用,在认真阅读产品说明及有关资料,了解其引脚分布及极限参数外,还应注意以下几个问题。

1、电源问题

(1)CMOS集成电路的工作电压一般在3-18V,但当应用电路中有门电路的模拟应用(如脉冲振荡、线性放大)时,最低电压则不应低于4.5V。由于CMOS集成电路工作电压宽,故使用不稳压的电源电路CMOS集成电路也可以正常工作,但是工作在不同电源电压的器件,其输出阻抗、工作速度和功耗是不相同的,在使用中一定要注意。

(2)CMOS集成电路的电源电压必须在规定范围内,不能超压,也不能反接。因为在制造过程中,自然形成许多寄生二极管,在正常电压下,这些二极管皆处于反偏,对逻辑功能无影响,但是由于这些寄生二极管的存在,一旦电源电压过高或电压极性接反,就会使电路产生损坏。

2、驱动能力问题

CMOS电路的驱动能力的提高,除选用驱动能力较强的缓冲器来完成之外,还可将同一个芯片几个同类电路并联起来提高,这时驱动能力提高到N倍(N为并联门的数量)。

3、输入端的问题

(1)输入端接长导线时的保护。

在应用中有时输入端需要接长的导线,而长输入线必然有较大的分布电容和分布电感,易形成LC振荡,特别当输入端一旦发生负电压,极易破坏CMOS中的保护二极管。其保护办法为在输入端处接一个电阻。

(2)输入端的静电防护。

虽然各种CMOS输入端有抗静电的保护措施,但仍需小心对待,在存储和运输中最好用金属容器或者导电材料包装,不要放在易产生静电高压的化工材料或化纤织物中。组装、调试时,工具、仪表、工作台等均应良好接地。要防止操作人员的静电干扰造成的损坏,如不宜穿尼龙、化纤衣服,手或工具在接触集成块前最好先接一下地。对器件引线矫直弯曲或人工焊接时,使用的设备必须良好接地。

(3) 输入信号的上升和下降时间不易过长,否则一方面容易造成虚假触发而导致器件失去正常功能,另一方面还会造成大的损耗。

对于74HC系列限于0.5us以内。若不满足此要求,需用施密特触发器件进行输入整形。

(4)CMOS电路具有很高的输入阻抗,致使器件易受外界干扰、冲击和静电击穿,所以为了保护CMOS管的氧化层不被击穿,一般在其内部输入端接有二极管保护电路。

输入保护网络的引入使器件的输入阻抗有一定下降,但仍在108Ω以上。这样也给电路的应用带来了一些限制:

(A)输入电路的过流保护。CMOS电路输入端的保护二极管,其导通时电流容限一般为1mA在可能出现过大瞬态输入电流(超过10mA)时,应串接输入保护电阻。例如,当输入端接的信号,其内阻很小、或引线很长、或输入电容较大时,在接通和关断电源时,就容易产生较大的瞬态输入电流,这时必须接输入保护电阻,若VDD=10V,则取限流电阻为10KΩ即可。

(B) 输入信号必须在VDD到VSS之间,以防二极管因正向偏置电流过大而烧坏。因此在工作或测试时,必须按照先接通电源后加入信号,先撤除信号后关电源的顺序进行操作。在安装,改变连接,拔插时,必须切断电源,以防元件受到极大的感应或冲击而损坏。

(C)由于保护电路吸收的瞬间能量有限,太大的瞬间信号和过高的静电电压将使保护电路失去作用。所以焊接时电烙铁必须可靠接地,以防漏电击穿器件输入端,一般使用时,可断电后利用电烙铁的余热进行焊接,并先焊其接地管脚。

(D)要防止用大电阻串入VDD或VSS端,以免在电路开关期间由于电阻上的压降引起保护二极管瞬时导通而损坏器件。

4、CMOS的接口电路问题

(1)CMOS电路与运放连接。当和运放连接时,若运放采用双电源,CMOS采用的是独立的另一组电源。若运放使用单电源,且与CMOS使用的电源一样,则可直接相连。

(2)CMOS与TTL等其它电路的连接。在电路中常遇到TTL电路和CMOS电路混合使用的情况,由于这些电路相互之间的电源电压和输入、输出电平及负载能力等参数不同,因此他们之间的连接必须通过电平转换或电流转换电路,使前级器件的输出的逻辑电平满足后级器件对输入电平的要求,并不得对器件造成损坏。逻辑器件的接口电路主要应注意电平匹配和输出能力两个问题,并与器件的电源电压结合起来考虑。下面分两种情况来说明:

(A)TTL到CMOS的连接。用TTL电路去驱动CMOS电路时,由于CMOS电路是电压驱动器件,所需电流小,因此电流驱动能力不会有问题,主要是电压驱动能力问题,TTL电路输出高电平的最小值为2.4V,而CMOS电路的输入高电平一般高于3.5V,这就使二者的逻辑电平不能兼容。为此可在TTL的输出端与电源之间接一个电阻R(上拉电阻)可将TTL的电平提高到3.5V以上。

(B)CMOS到TTL的连接。CMOS电路输出逻辑电平与TTL电路的输入电平可以兼容,但CMOS电路的驱动电流较小,不能够直接驱动TTL电路。为此可采用CMOS/TTL专用接口电路,如CMOS缓冲器CC4049等,经缓冲器之后的高电平输出电流能满足TTL电路的要求,低电平输出电流可达4mA。实现CMOS电路与TTL电路的连接。 需说明的时,CMOS与TTL电路的接口电路形式多种多样,实用中应根据具体情况进行选择。

5、输出端的保护问题

(1)MOS器件输出端既不允许和电源短接,也不允许和地短接,否则输出级的MOS管就会因过流而损坏。

(2)在CMOS电路中除了三端输出器件外,不允许两个器件输出端并接,因为不同的器件参数不一致,有可能导致NMOS和PMOS器件同时导通,形成大电流。但为了增加电路的驱动能力,允许把同一芯片上的同类电路并联使用。

(3)当CMOS电路输出端有较大的容性负载时,流过输出管的冲击电流较大,易造成电路失效。为此,必须在输出端与负载电容间串联一限流电阻,将瞬态冲击电流限制在10mA以下。

-

集成电路

+关注

关注

5317文章

10678浏览量

353095 -

CMOS

+关注

关注

58文章

5142浏览量

233266

原文标题:CMOS电路多余输入端悬空,会造成逻辑混乱,该如何处理?

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何处理CMOS电路的逻辑混乱?

如何处理CMOS电路的逻辑混乱?

评论