在数据采集系统中,所设计的系统应具有通用性,可根据不同的数据采集对象,产生不同的采样频率;或者系统处于不同的运动情况时,能够动态改变采样频率,即数据采集系统应当具有改变采样频率的能力。传统的数据采集系统,一般都是固定频率的数据采集,很难应用于其它采样频率的场合。为了使所设计的系统适用于不同的场合,具有广泛的适应性,系统必须具有在线改变采样频率的方法。可编程时钟发生器芯片ICD2053B提供了系统动态改变频率的方法,其动态时钟输出频率范围从391kHz到100MHz(TTL电平)或391kHz到90MHz(CMOS电平),具有较宽的频率范围,在系统中采用ICD2053B能很好地解决上述问题。ICD2053B提供完全用户可编程的锁相环特性,锁相环振荡器输入由外部参考时钟(1MHz~25MHz)或外部晶振(2MHz~24MHz)提供。其二线串行接口便于对输出频率进行编程控制,具有三态输出控制使能。5V供电、低功耗、小体积又使其适宜于功耗和空间要求高的应用场合。它所具有的动态改变输出频率的能力,给设计得提供了灵活的设计自由度。

1 ICD2053B的结构及工作原理

1.1 引脚功能表及内部结构图

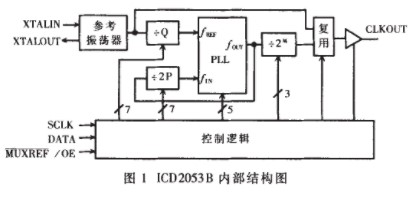

ICD2053B的内部结构如图1所示,引脚功能如表1所示。

表1 ICD2503B引脚功能表

1.2 ICD2053B的寄存器

ICD2053B包含两个寄存器:控制寄存器和编程寄存器。

这两个寄存器使用协议字011110来区分是控制寄存器数据还是编程寄存器数据。所有要发送的其它数据(除协议字外)在连续3个1之后,不论原来其后的数值是1还是0必须插入一个0,来区分是协议字还是数据。所有要编程的串行字从最低位开始串行地移入,当SCLK从低到高跳变时,将数据移入到可编程寄存器中。一旦协议字检出后,前面已移入的8位数据就传递到控制寄存器中,然后控制命令立刻被执行。

1.2.1 控制寄存器

当要写入的数据写入到控制寄存器时,必须包含协议字011110,用来识别所写入的数据为控制寄存器数据。

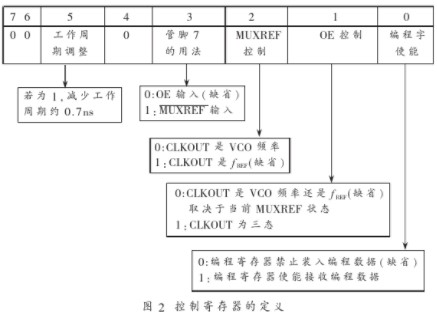

控制寄存器用来控制ICD2053B的非频率特性设置,它是一个8位的寄存器,其含义如图2所示。

控制寄存器数据的写入从控制字的低位(位0)开始,一直到控制字的高位(位7),然后是6位的协议字写入到寄存器中,故控制寄存器的设置其需14位数据。

在上电后,控制寄存器装入缺省值00000100,即MUXREF控制位设置为1,强制CLKOUT输出为参考频率fREF,编程寄存器禁止装入,芯片管脚7是输出使能管脚。

1.2.2 编程寄存器

按照所需要的输出频率,将22位的编程字装入到编程寄存器,用以实现输出频率的更改。由于协议字为011110,在传送编程数据时,凡连续出现3个1,在其后便添一个“虚”0,以避免混淆;在接收端凡连续收到3个1,就将其后的零丢掉,故装入的数据要完成“位填充”功能。由于这个原因,实际的编程字的长度可以为22到27位。编程寄存器各字段含义如表2所示。

表2编程寄存器定义

可编程振荡器的频率fvco由下式确定:

fvco=2×fREF×(P+3)/(Q+2)

式中,fREF为参考频率(1MHz~25MHz)。

Fvco的频率值必须保证处在50MHz和150MHz之间。因此对于输出频率低于50MHz,fvco必须设法处于上述限制之内,可通过复用(M)字段的设置来实现该功能,M初值为000。首先将所希望的输出频率倍频,作为新的输出频率,M值增1,若仍未处于上述范围,循环直至满足要求为止(M≤7)。由于倍频所希望的输出频率,实际的输出频率就要进行相应的分频,最大的分频值为128,即输出频率fout由下式确定:

fout=fvco/2 m

指针(I)字段用来使压控振荡器VCO预置到适当的频率范围。若fvco在50~80MHz,I为0000;若fvco在80~150MHz内,I为1000。注意,此处仅指压控振荡器频率fvco。而非所希望的输出频率。

如果压控振荡器的频率正好处在80MHz,则推荐使用对应高频率范围的设置,即I为1000。

1.2.3 VCO编程的限制

编程时有以下3个主要的限制:

(1)50MHz≤fvco≤150MHz

(2)1≤P≤127

(3)1≤Q≤127

对于上述限制,要在最优速度、最低噪声和VCO稳定性等因素中,折衷考虑。

2 频率调整过程

当改变频率到一个新频率时,由于串行字的变化,输出信号频率会产生频率跳变。为了避免这种情况发生,可以利用控制寄存器中MUXREF的特性。MUXREF使得参考时钟多路复用,无跳变地切换,作为输出时钟,即当VCO寻求新的编程值时,它使输出时钟频率维持在固定的参考时钟频率上。

ICD2053B初始化或调整新频率的步骤如下:

(1)装入控制寄存器控制字,允许编程寄存器装入数据,使能MUXREF功能,使输出频率稳定在参考频率上,且这个过程保证无跳变。控制字如下:

控制字 011110 0000X101 --- LSB

协议字 要写入的控制寄存器控制字

管脚7的用法由用户定义,用X表示。

注意:所有的数据都从低位移入,首先移入的是控制字的最低位,协议字紧跟着控制寄存器的控制字之后输入到寄存器中。

(2)装入编程寄存器编程字,使用“位填充”,最多可得27位的编程字。

(3)装入控制寄存器控制字,使能MUXREF功能,禁止编程寄存器数据的装放。该过程将编程字装入到编程寄存器中,保持输出在参考频率上,同时进行新频率的建立。控制字如下:

控制字 011110 0000X100

(4)等待至少10ms,使压控振荡器VCO的频率稳定在新的频率值上。

(5)装入控制寄存器控制字,使能芯片输出新频率,该过程保证无跳变。控制字如下:

控制字 011110 0000X000

总之,为了使芯片通过编程输出一个新频率,该芯片需要三个控制字加上一个编程字共同来实现。

3 ICD2053B在数据采集系统中的应用

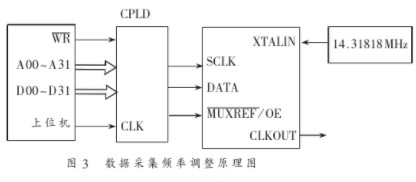

在我们所设计的通用数据采集系统中,系统可以在线改变采样频率,具有动态改变采样频率的能力。该通用数据采集系统选用可编程时钟发生器芯片ICD2053B,提供大范围的采样频率(391kHz~100MHz)。ICD2053B的编程连接仅需要两条线,即SCLK(2)、DATA(4)。利用ICD2053B动态改变采样频率的电路原理图如图3所示。

在该系统中,参考晶振频率为14.31818MHz。可编程逻辑器件CPLD作为上位机与ICD2053B的接口,实现可编程时钟发生器串行时钟和编程数据的串行输入控制功能。CPLD的主时钟由上位机提供,经分频后产生所需的串行时钟SCLK,控制移位寄存器,串行移出所需的编程数据。为了帮助实现计算,上位机提供系统工作的驱动程序,根据用户的参考输入频率和所希望的输出频率,产生适当的编程寄存器编程字。

当用户输入所希望的输出频率时,驱动程序自动计算所需的编程字,同时考虑到“位填充”的要求,产生实际的编程字。然后在上位机的控制下,经上位机写入到可编程逻辑器件CPLD对应的寄存器中,作为触发信号,启动频率调整状态机。

按照频率调整过程,该状态机的状态0为空闲状态;状态1为在串行时钟SCLK的控制下,将控制字01111000000101由低位开始串行移入可编程芯片中;状态2为在串行时钟的控制下,将寄存器中存放的编程字串行移入到可编程芯片中,此时要增加超过22位编程数据的位计数器,以便正确地将编程字移入;状态3为在串行时钟的控制下,将控制字01111000000100由低位开始串行移入可编程芯片中;状态4为在串行时钟的控制下,延时等待10ms,进入下一状态;状态5为在串行时钟的控制下,将控制字0111100000000由低位开始串行移入可编程芯片中,使芯片输出所希望的新频率,同时进入状态0,等待下一次的频率调整。

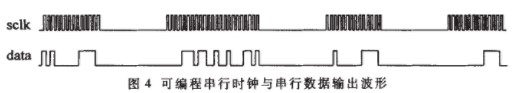

串行时钟并不是一直输出,只有在对ICD2053B进行编程调整输出频率时,才有串行时钟输出。即串行时钟在非编程状态时输出为零,在编程状态时才输出可编程时钟。若产生39.5MHz的输出频率,考虑位填充的实际编程字为589370H,其相应的可编程时钟与串行数据输出的波形如图4所示。

在该数据采集系统中,采用可编程时钟发生器芯片ICD2053B,动态调整采样频率,使得系统具有通用性。系统硬件设计简单,通过串行数据编程,可在线改变采样频率。而在频率调整过程中,无频率跳变,输出时钟频率维持在固定的参考时钟频率上,特别适用于对采样频率调整要求高的场合。

-

芯片

+关注

关注

446文章

47746浏览量

409039 -

cpld

+关注

关注

32文章

1243浏览量

168279 -

计数器

+关注

关注

32文章

2121浏览量

92944

发布评论请先 登录

相关推荐

基于FPGA的高速数据采集系统该怎么设计?

用ARM和FPGA怎么设计便携式人工地震数据采集系统?

基于CPLD的多通道数据采集系统设计

基于CPLD与单片机的高速数据采集系统

基于CPLD和FIFO的多通道高速数据采集系统的研究

CPLD芯片ICD2053B的原理构造及在数据采集系统中的应用

CPLD芯片ICD2053B的原理构造及在数据采集系统中的应用

评论