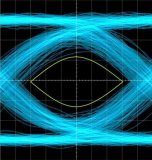

眼图,是由于示波器的余辉作用,将扫描所得的每一个码元波形重叠在一起,从而形成眼图。本文将带领大家了解PCB上的眼图是什么,眼图是怎样形成的,眼图中包含有哪些信息,如何根据眼图情况分辨信号质量。

眼图的定义眼图是指利用实验的方法估计和改善(通过调整)传输系统性能时在示波器上观察到的一种图形。观察眼图的方法是:用一个示波器跨接在接收滤波器的输出端,然后调整示波器扫描周期,使示波器水平扫描周期与接收码元的周期同步,这时示波器屏幕上看到的图形像人的眼睛,故称 为 “眼图”。从“眼图”上可 以观察出码间串扰和噪声的影响,从而估计系统优劣程度。另外也可以用此图形对接收滤波器的特性加以调整,以减小码间串扰和改善系统的传输性能。

tips

2

眼图的形成

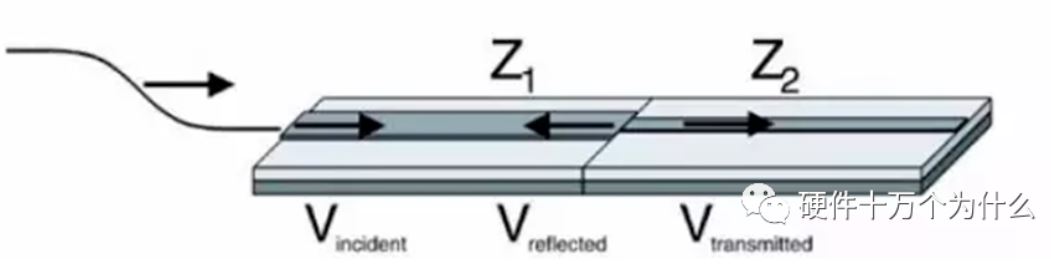

对于数字信号,其高电平与低电平的变化可以有多种序列组合。以3个bit为例,可以有000-111共8中组合,在时域上将足够多的上述序列按某一个基准点对齐,然后将其波形叠加起来,就形成了眼图。如下图。对于测试仪器而言,首先从待测信号中恢复出信号的时钟信号,然后按照时钟基准来叠加出眼图,最终予以显示。

tips

3

眼图中包含的信息

对于一幅真实的眼图,如下图,首先我们可以看出数字波形的平均上升时间(Rise Time)、下降时间(Fall Time)、上冲(Overshoot)、下冲(Undershoot)、门限电平(Threshold/Crossing Percent)等基本的电平变换的参数。

上升时间(Rise Time):脉冲信号的上升时间是指脉冲瞬时值最初到达规定下限和规定上限的两瞬时之间的间隔。除另有规定之外,下限和上限分别定为脉冲峰值幅度的10%和90%。

下降时间(Fall Time):脉冲信号的下降时间是指从脉冲峰值幅度的90%下降到10%所经历的时间间隔。

上冲(Overshoot)也叫过冲就是第一个峰值或谷值超过设定电压,主要表现为一个尖端脉冲,并且能导致电路元器件的失效。

下冲(Undershoot)是指下一个谷值或峰值。过分的过冲能够引起保护二极管工作,导致过早地失效。过分的下冲能够引起假的时钟或数据错误。

门限电平(Threshold/Crossing Percent)是指在系统传输特性劣于某一特定误码率的情况下,收信机所能达到的最低接收电平;

tips

4

如何根据眼图情况分辨信号质量

信号不可能每次高低电平的电压值都保持完全一致,也不能保证每次高低电平的上升沿、下降沿都在同一时刻。由于多次信号的叠加,眼图的信号线变粗,出现模糊(Blur)的现象。所以眼图也反映了信号的噪声和抖动:在纵轴电压轴上,体现为电压的噪声(Voltage Noise);在横轴时间轴上,体现为时域的抖动(Jitter)。如下图示。

当存在噪声时,噪声将叠加在信号上,观察到的眼图的线迹会变得模糊不清。若同时存在码间串扰 , “眼睛”将 张开得更小。一般眼图的眼睛睁得越大,眼图眼高越高,代表信号质量越好。做信号仿真可以获取眼图情况,然后根据眼图情况判断信号的质量,如果眼图情况不好,可以调整硬件设计或者PCB设计,使眼图眼高变高,保证生产出的产品信号质量。

学习了这些知识是不是对PCB上的眼图有了更深层次的了解呢,赶紧应用到您自己的项目当中去吧!

-

pcb

+关注

关注

4216文章

22446浏览量

385271 -

示波器

+关注

关注

110文章

5637浏览量

181676 -

眼图

+关注

关注

1文章

63浏览量

21009

原文标题:干货篇 || PCB设计中眼图到底有什么用?

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

NUC123的USB外设到底有没有DMA功能?

AD9781或是AD9783芯片的DCOP/DCON信号有什么用?

PCB设计有必要去除死铜吗?

pcb钢网层是哪层大揭秘,这层到底有什么作用?

npu是什么意思?npu芯片是什么意思?npu到底有什么用?

NUC123的USB外设到底有没有DMA功能?

PCB设计到底要不要去除孤铜?

board中的Kconfig到底有什么用?

PCB上的眼图是什么?PCB设计中眼图到底有什么用?

PCB设计中眼图到底有什么用?

PCB设计中眼图到底有什么用?

评论