“XX工,麻烦你把这组数据线的间距调大一些,我担心串扰会比较大”

“间距我已经按照3H处理了而且布线空间也没办法调整了”

“这个DDR4是要跑2400M的,麻烦您调整一个合适的间距,尽量不要出问题”

但是怎样才是合适的符合设计要求的间距,在layout工程师眼里一直都是一个玄学的命题,只能放飞想象的翅膀,而不是一个可以用数字量化的结果。就好像串扰,也是一个抽象的世界,所以每每遇到这种问题,大家就只能佛系一点啦。

对于串扰,我们可能了解是怎么产生的,以及变化的趋势,但实际上,在遇到间距太近没有空间调整,或者双带线层叠的时候,我们能做的就是尽量拉开间距,却没有太直观的办法评估多大的间距会是比较符合要求的。在没有测试参数,没有仿真结果的情况下,是不是只能靠拍脑袋了呢?此时,Allegro17.2中的功能——线间耦合串扰分析“duang”就适时出场。这个功能可以帮layout工程师去衡量间距和串扰之间的平衡(编者注:即评估间距对串扰的影响),用具体的参数告诉大家,怎样的间距才是符合设计要求的。还是一样用一个例子来说明新功能的实用性。

如下图所示DDR3信号,工作频率为1600Mbps,按照客户要求设置了比较严格的等长要求±5mil,由于空间的影响,部分地方间距压缩到5mil才能完成时序等长,这个间距和我们平时的设计规范是违背的(编者注:即平时的设计规范是超要求的),这种时候就需要准确的数据,用严谨的态度去说服客户修改等长要求,下面我们用线间耦合串扰分析去看一下5mil的间距对于信号的影响大不大。

首先选择Coupling Workflow,开始设置其他参数。选择需要分析的网络,设置耦合阈值为2%,意味着耦合率为2%以下时忽略不计。一般的遵循的规则是耦合率应该为5%以下,当耦合率高于5%以上时,信号间距就需要调整了。设置比较简单,傻瓜式操作,对于英语渣的我而言,可以说是非常的人性化了。选择start analysis。

结果也是通过两种方式显示:coupling Vision,比较直观的一种方式,把鼠标放置在相应的线段上时,也会显示相应的耦合系数。

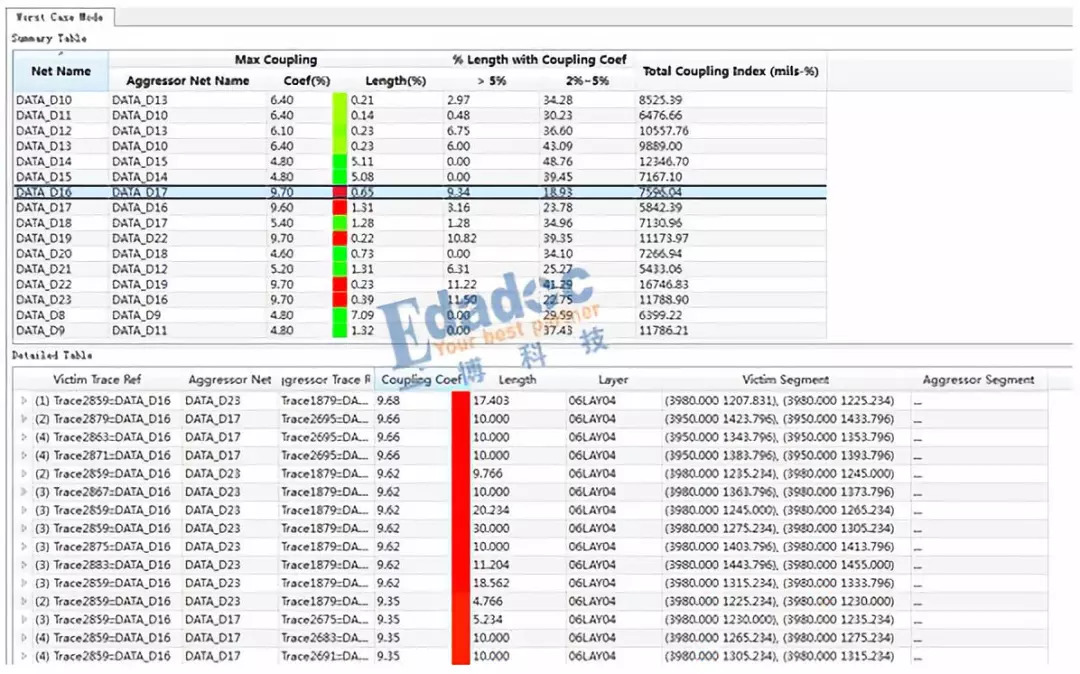

另一种结果显示方式是coupling table,数据比较清晰具体,主要关注的是最大耦合系数以及耦合系数大于5%的部分线长比例。

从上面的结果可以看到,部分网络的耦合系数达到9.7%,串扰太大,对信号质量可能影响会比较大。但这些地方都比较短,比较容易调整,所以可以选择适当放宽等长规则到±25mil,把间距拉开到9mil,这是可以满足时序,调整也比较小的一种方式,结果如下图,耦合系数均在5%以下。

这种数据让我们在设计的时候,能够清楚的了解到自己板子的实际情况,不需要靠想象去完成板子的修改,也有直观的数据指导修改,修改点清晰明了,对于提升设计效率以及设计的准确性是有很大帮助的。

-

DDR3

+关注

关注

2文章

268浏览量

41770 -

PCB设计

+关注

关注

392文章

4568浏览量

83178 -

allegro

+关注

关注

41文章

625浏览量

144019 -

串扰

+关注

关注

4文章

183浏览量

26776 -

可制造性设计

+关注

关注

10文章

2062浏览量

15306 -

华秋DFM

+关注

关注

20文章

3481浏览量

3898

原文标题:怎样才是符合设计要求的线间距?——Allegro17.2新功能

文章出处:【微信号:CadencePCB,微信公众号:CadencePCB和封装设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何设计符合要求的间距?避免串扰Allegro17.2新功能实例分析

如何设计符合要求的间距?避免串扰Allegro17.2新功能实例分析

评论