据国外媒体援引业内人士的观点指出,由于10纳米以下芯片的生产工作需要大量资本投入,大量芯片制造商纷纷基于成本考虑选择将业务重点继续放在现有14/12纳米工艺上,同时减缓了自己对更先进纳米工艺的投资脚步。

众所周知,10纳米以下芯片制造工艺的研发成本非常高昂。许多芯片厂商也意识到了这一问题,并开始考虑如此高的研发投入是否能够给自己带来长远收益。

海思(HiSilicon)集团不久前曾表示,公司将斥资3亿美元研发基于7纳米工艺的下一代SoC芯片产品。然而,包括高通和联发科(MediaTek)都已经通过推出新的14/12纳米芯片解决方案加强自己在中高端市场的竞争力。

消息人士指出,在目前的市场环境下,许多企业都对向7纳米芯片技术转型是否必要心存疑虑。

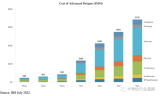

除了台积电和三星之外,其他厂商暂缓跟进7纳米的主要原因是市场需求尚未达到。目前7纳米的良品率低、流片成本高,且现有产品足以支持主流应用,并不需要更高的性能。如果采用7纳米工艺制造,芯片制造商大约需要每年1.2-1.5亿套的产量才能够盈亏平衡,弥补研发成本。目前看来,只有苹果、三星、高通和联发科能够达到这样的生产规模。

报道称,高通和联发科已将自己的7纳米芯片解决方案推出时间从2018年推迟到了2019年,预计将同自己的智能手机5G解决方案一同推出市场。分析人士认为,在5G设备正式投入商用前,高通和联发科继续专注于中高端市场是一个合适的举措,也同公司致力于满足消费者当下实际需求的理念相一致。

目前,台积电和三星都已经公布了自己7纳米技术的演进路线图。中国***芯片代工厂商联电(UMC)则已经将自己的投资重点转移到已经成熟和拥有技术优势的产品线上,同时进一步弱化了同竞争对手有关更先进芯片技术的竞争。该公司希望,通过这一战略转型加强现有产品线竞争力,同时提高公司运营利润。

需要指出的是,全球第二大晶圆代工厂芯片制造商GlobalFoundries上月宣布,公司放弃了开发下一代半导体技术的宏伟计划,转而将资源聚焦到现有技术上。这意味着GlobalFoundries将会裁掉5%的员工,也意味着下一代半导体领域剩下的厂家就只有苹果的现任芯片代工商台积电和前任代工商三星。

对此,GlobalFoundries CTO嘉里-派顿(Gary Patton)坚称,公司做出这一决定不是因为技术问题,而是在谨慎考虑了7纳米工艺的商业机会和财务问题后做出的选择。

“现有14/12纳米还有很大的改进空间,改进现有技术所需的资源比研发7纳米甚至5纳米工艺要少得多。而且即使到2022年,四分之三的芯片市场仍然只需要12纳米工艺。”派顿当时解释道。

-

芯片

+关注

关注

446文章

47746浏览量

409041 -

高通

+关注

关注

76文章

7156浏览量

187854 -

联发科

+关注

关注

55文章

2537浏览量

252611 -

7纳米工艺

+关注

关注

0文章

5浏览量

2844

原文标题:成本过高致大量芯片厂暂缓先进工艺转型!

文章出处:【微信号:CSF211ic,微信公众号:中国半导体论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

芯片键合:芯片与基板结合的精密工艺过程

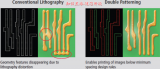

数字后端先进工艺知识科普

HRP晶圆级先进封装替代传统封装技术研究(HRP晶圆级先进封装芯片)

什么是合封芯片工艺,合封芯片工艺工作原理、应用场景、技术要点

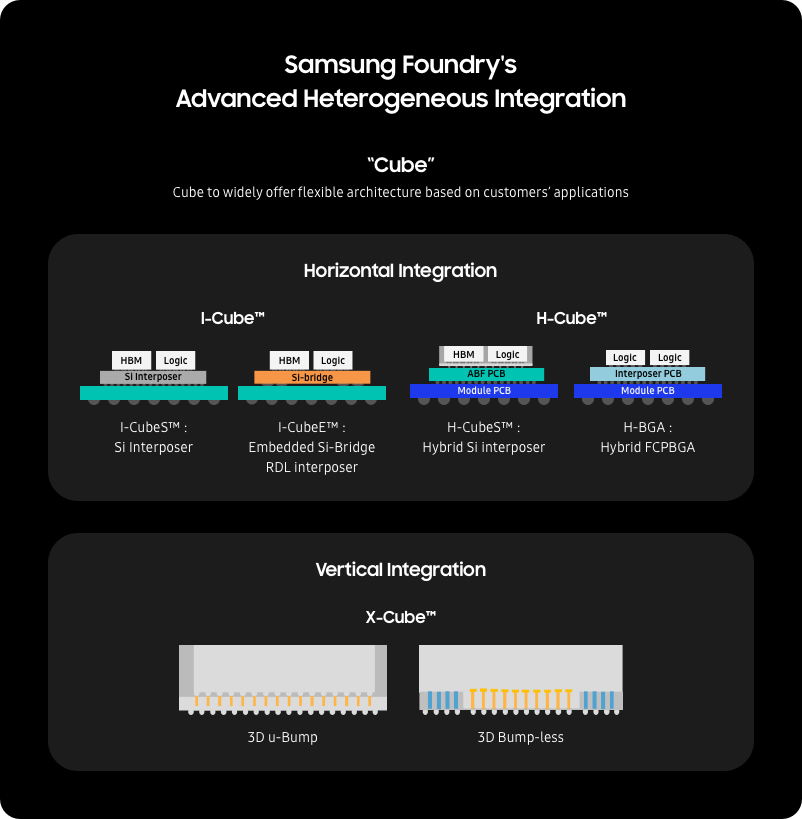

晶圆厂拼的不只是先进逻辑工艺节点,异构集成技术不可小觑

芯片的真实成本是多少?

使用先进工艺的芯片设计成本是多少

苹果a17芯片成本多少 苹果a17芯片几纳米工艺

明年全系a17芯片都将量产,A17芯片的成本将更低

2nm芯片设计成本曝光

一文解析Chiplet中的先进封装技术

成本过高致大量芯片厂暂缓先进工艺转型!

成本过高致大量芯片厂暂缓先进工艺转型!

评论