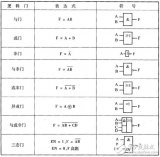

CMOS级逻辑电路实现综述

CMOS逻辑电路,分两部分,上拉部分,下拉部分。上拉部分由PMOS管电路构成,下拉部分由NMOS管电路组成,如下。上下拉,形成互补。

由前面的基础可知,CMOS只能实现基本逻辑的非,比如或逻辑,与逻辑,如果不加反相器,CMOS只能实现或非,与非逻辑。原因就是上拉逻辑只能用PMOS实现,下拉逻辑只能由NMOS实现,而PMOS的导通需要输入信号为0,NMOS导通需要输入信号为1。

既然如此,我们在用CMOS实现逻辑电路时,一般可以照如下顺序去做:

1. 可以先将其整体先加上一个非,作相应的逻辑转化。

2. 上拉逻辑中各个PMOS,与操作为并联,或操作为串联。

3. 下拉逻辑中各个NMOS,与操作为串联,或操作为并联。

比如我们想从CMOS层去实现逻辑 OUT = D+A*(B+C) (减号“-”表示取反(非)操作,“+”表示或,*表示与)。

设计过程如下:

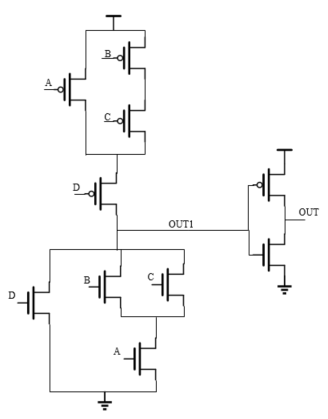

1. OUT = - ( -(D+A*(B+C)) )

2. OUT1 =-(D+A*(B+C))

3. OUT = -OUT1

对于OUT1 = -(D+A*(B+C)),正好是逻辑整体上带了个非。

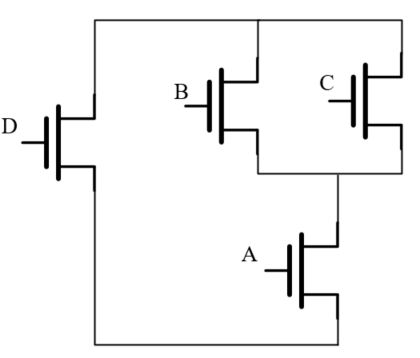

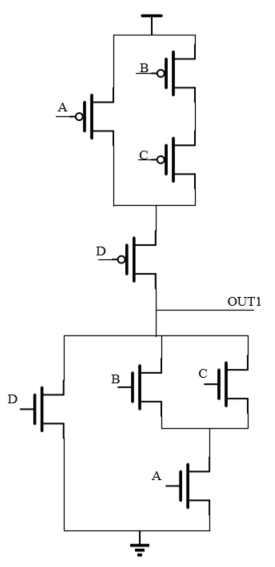

故对于上拉逻辑:

或操作为串联,从而输入B,C接到的PMOS之间为串联。

与操作为并联,故输入A接到的PMOS跟B,C或逻辑之间为并联。

或操作为串联,故D与A*(B+C)的PMOS逻辑为串联。

对于下拉逻辑与上拉逻辑正好相反:

或操作为并联,从而输入B,C接到的NMOS之间为并联。

与操作为串联,故输入A接到的NMOS跟B,C或逻辑之间为串联。

或操作为并联,故D与A*(B+C)的NMOS逻辑为并联。

从而得到OUT1 =-(D+A*(B+C)) 的CMOS实现如下:

OUT = -OUT1,故得最终答案如下:

当然,在MOS管级别还可以做一些优化,比如MOS管级别的逻辑优化,MOS管栅源共用,晶体管尺寸调整,重新安排各个输入的上下顺序等等,都可以在MOS管级别使得电路的时序与面积功耗等得到优化,但这不是我们的重点,一般对于全定制IC设计会从MOS管级开始考虑电路的实现。这里我们只是对其做一个了解。

我们今后的重点将会注重于门级以上的电路实现与优化,特别是到了Verilog描述,主要着重于数据流级,行为级描述。

-

CMOS

+关注

关注

58文章

5136浏览量

233232 -

逻辑电路

+关注

关注

13文章

466浏览量

42180

原文标题:CMOS级逻辑电路实现综述

文章出处:【微信号:LF-FPGA,微信公众号:小鱼FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

集成逻辑电路、组合逻辑电路

【原创】组合逻辑电路详解、实现及其应用

数字系统的基本算法与逻辑电路实现

CMOS逻辑电路,CMOS逻辑电路是什么意思

组合逻辑电路实验原理

CMOS级逻辑电路实现综述

CMOS级逻辑电路实现综述

评论