人工智能(ArtificialIntelligence,AI)的概念早在上个世纪五十年代已经出现。但是直到二十一世纪,得益于深度学习算法的发展、硬件运算力的提升、以及越来越多可供训练的样本数据的获得,人工智能才得到了真正的爆发。尤其是在图像、视频和语音识别方面的应用,人工智能表现得愈发强大。支持强大的深度学习算法的背后,所依靠的是集成电路芯片的运算能力。在性能和灵活性的取舍中,CPU、GPU、FPGA和ASIC分别有着不同的表现。其中定制的AI加速芯片往往能够通过深度的软硬件结合达到极致的能效比和吞吐量。本文分析了专用AI芯片的特点,实现过程中性能、功耗、面积等方面的挑战,以及应对这些挑战的解决方案。

人工智能是一个非常广泛的领域,也并不是一个新的概念。早在上世纪50年代,也就是计算机诞生不久,就已经有不少学者开始了这方面的研究,发展出了非常多的分支科。近十年来,这一名词更多地被提及则是因为深度学习领域取得的巨大进展,掀起了从算法、软件层面一直到硬件、芯片层面的不断创新。

Source:https://www.edureka.co/blog/what-is-deep-learning

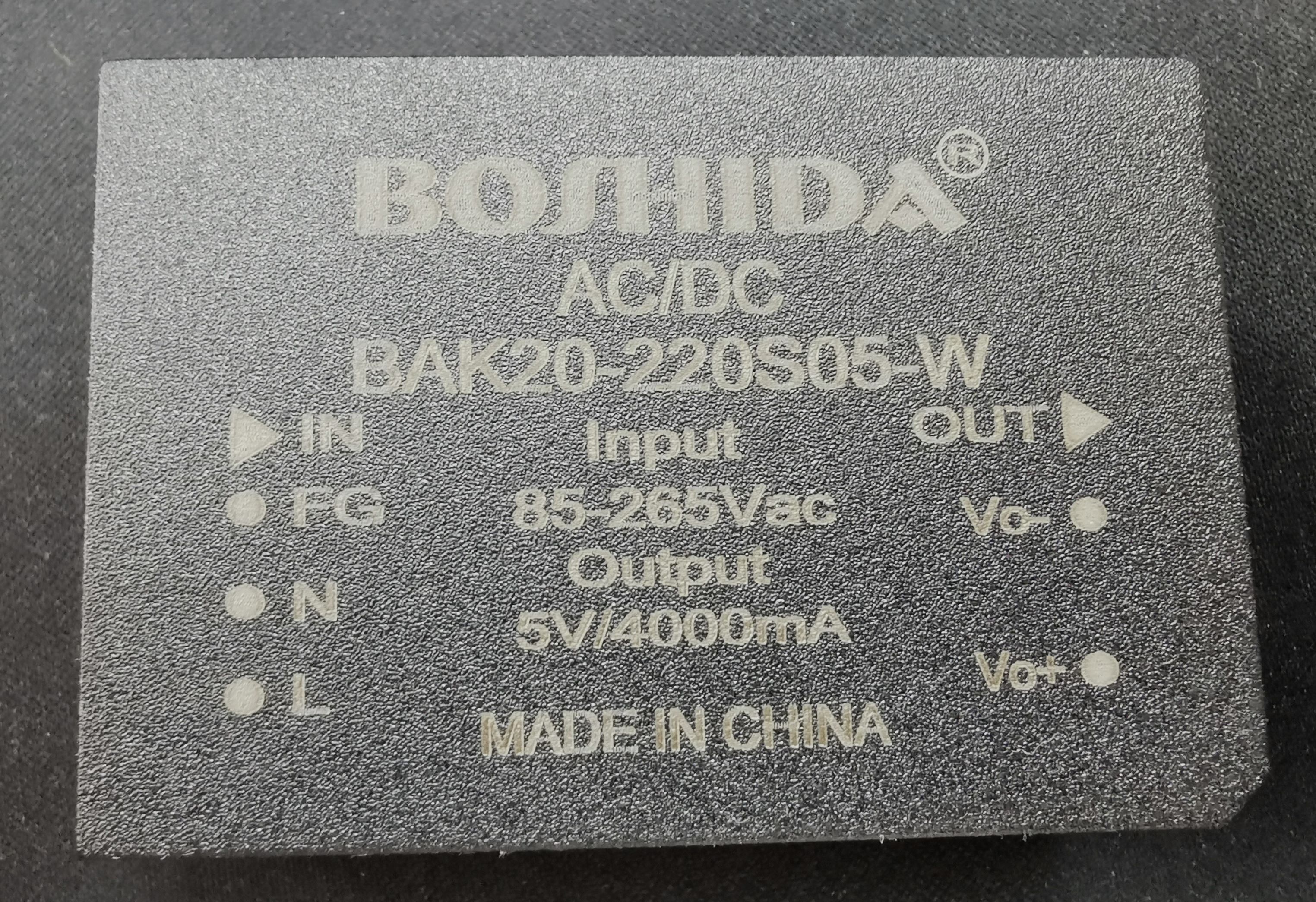

图一

图一展示了人工智能涉及到的三个领域之间的关系:

1.人工智能(Artificial Intelligence,AI),是研究使计算机来模拟人的思维过程和智能行为的学科,是最广义的一个概念,包括模式识别、规划推理、复杂系统、专家系统、模糊控制、自然语言处理等非常多的研究领域。但是现阶段能够实现的人工智能实际上并不真正拥有思维,只是表现起来类似人的行为,仍然属于弱人工智能的范畴。

2.机器学习(Machine Learning,ML),是人工智能的一个分支,研究如何让计算机不通过显式的编程而通过数据进行自主学习的能力。人工神经网络是这一领域众多算法的其中一个,一度并没有得到比较大的发展,直到深度神经网络算法的出现。

3.深度学习(Deep Learning,DL)是机器学习的一个分支,同时也是二十一世纪人工智能爆发的最大的推手。深度学习是利用深度神经网络(DeepNeuralNetwork,DNN)来解决特征表达的一种学习过程。在图像、视频、语音识别领域,最新的深度学习算法已经做到了比人类更好的表现。这来源于深度神经网络更多级数的隐藏层,如图二所示:

Source:https://www.quora.com/What-is-the-difference-between-Neural-Networks-and-Deep-Learning

图二

这些隐藏层互相连接,使得输入信息的特征能够被识别、提取和传播。如图三所示,过去几年主流的神经网络的层数和所需参数的数量呈现快速增长的趋势。比如,2015年的Residual Net可以达到152层,所有参数加起来超过1.5亿个。

Source:http://speech.ee.ntu.edu.tw/~tlkagk/talk.html

图三

这带来的问题主要是什么呢?是计算量的激增!神经网络的训练是通过用大量的样本数据,对每一个参数做梯度下降、反向传播等迭代计算,从而逐步确从而逐步确定所有的参数值。对于庞大参数量的神经网络,可想而知计算量会是一个天文数字。即使是训练完的模型想要使用,也必然躲不开大量的卷积、矩阵乘法等运算,计算量依然不小。

一、人工智能芯片的目的

为了在可接受的功耗、成本限制下,解决深度学习巨大计算量的问题,人们开始设计研究专用的人工智能加速芯片。需要注意的是,人工智能芯片(或AI芯片)并不是芯片本身具有智能,而是用于加速深度学习算法的一种专用加速芯片。那么我们为什么不用传统的CPU来计算呢?这就涉及到性能和灵活性之间的矛盾。

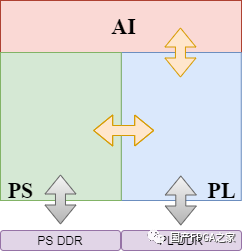

图四列出了几种不同类型用于计算的芯片。横轴是性能,纵轴是灵活性。

Source: https://cloud.tencent.com/developer/article/1006018

图四

前面我们已经知道,深度学习巨大的运算量,大多数是乘法和加法,那么普通的CPU就足以完成任务。事实上也确实是这样的。早期在神经网规模不大的时候人们的确是用CPU进行运算的。但是CPU有一个很大问题,就是运算性能比较低。相对于动则几百万参数的神经网络来说,计算能力严重不足。这是因为CPU的强项是并不是运算,而是逻辑,比如分支预测。CPU作为通用处理器灵活性是极佳的,不考虑性能的话,理论上可以运行任意结构的深度学习算法。

GPU大规模的并行运算使得其计算能力显著高于CPU。并且GPU的设计也使得它可以承担通用的科学计算,具有不错的灵活性。但是这些通用性也使得它在功耗上的表现并不能令人满意,同时成本也非常高昂。

要追求极致的功耗、性能、成本,只能为深度学习算法量身定制专用的加速芯片,即ASIC。由于是专用芯片,几乎就没有太多的灵活性了。AI芯片所有的软硬件优化都是为了某些特定的深度学习算法所定制的。但是也正是由于专用的原因,可以不用考虑那些为了通用性所作出的妥协,提高性能、功耗方面的表现。

当然还有一种为大家所熟知的方案,就是FPGA,试图在性能和灵活性当中找到一个新的平衡点。

所以需不需要AI芯片?其实是性能和灵活性的一种权衡。当我们需要计算更快、功耗更小、成本更低的芯片的时候,AI芯片就是我们唯一的选择。

需要注意的是,这里所说的性能,指的并不是只我们通常所说的“主频”。它包括两方面的考量。

首先是能效,指的是,在一定的功耗下,单位时间能提供的运算次数。

其次是吞吐量。深度学习算法主要的计算是矩阵的乘法、加法。这种极其规律的算法本身就是高度结构化的。所以人们充分利用这种结构化,提高硬件的效率和并行度,使得在主频相同的情况下,数据的吞吐量大幅提高。

二、人工智能芯片的应用

在很多场景下,即使是终端设备,我们也是需要这样的专用AI芯片的。比如无人驾驶汽车,并不能依赖于数据上传服务器,计算完成后再下载结果。汽车需要实时的、极低延迟的反应。再比如终端设备,它的特性决定了我们不可能使用大功耗的GPU,同时对芯片成本也有比较严格的要求。

人工智能芯片的应用场景可以分为以下4种情形,如图五所示。

图五

纵轴分为推理(Inference)和训练(Training)。横轴分为终端(Device)和云端(Cloud)。其中终端推理和云端训练是应用最为广泛的两个场景。不仅是传统互联网和半导体巨头们,近年来涌现了众多的初创公司在这AI芯片这个领域发力。其中包括越来越多的中国的初创公司正在进入这个市场。

从市场划分来看,又可以分为下面五个方向,如图六所示(数据来源47家AI初创公司)。

·视觉增强(含安防监控)

·深度学习

·语音识别

·区块链

·云

图六

三、人工智能芯片实现的挑战

人工智能芯片在失去一些灵活性的条件下,尽可能达到更高的能效、吞吐量,更低的延迟和成本。因此从指标上来说,AI芯片实现过程中的挑战依然来源于:

1.性能(Performance)

2.功耗(Power)

3.面积(Area)

但是AI芯片的特点使得我们可以观察到它与其他类型芯片不同的一些挑战。结合这一特点,所应用的实现方法也更具有针对性。

1.性能的挑战自然是源于对AI芯片极致指标的追求。

由于AI芯片重运算和流水线设计的特征,加上众多的旁路设计,时序路径上,数据通路(Datapath)的长短差异非常明显。到达同一个寄存器的路径有的很长但有的很短。这都导致当把时钟频率推到极限的情况下,时序非常难以收敛。同时,由于芯片面积的极致优化,会导致density和congestion变得更高,使得时序优化捉襟见肘。无论是buffer的插入、cell的upsize都受到空间的局限。对于Setup Check来说,useful skew是必不可少的优化手段,如图七所示。

图七

但是useful skew的使用,在优化了setup timing的同时,大量的时钟偏斜也导致hold check变得更加难以修复。

在面积紧缩的条件下,工具势必不得不通过辗转腾挪,把绕线资源紧缺,也就是congestion严重的地方的standard cell推开,使其变得稀疏来缓解congestion的问题。而绕线资源不那么紧缺的地方,standard cell的密度就相应变得更高。而这些区域,hold timing的修复会变得更为困难,因为修hold 通常是通过增加delay cell来实现的,需要足够的空间。

制约性能的挑战还包括时钟树带来的影响。AI芯片大量的寄存器堆使得它需要一个足够大的时钟树来驱动这些同步电路。当芯片density比较低的时候,时钟树的插入不会带来太大的影响。但是极致的面积要求导致哪怕是几千个buffer的插入,也会对timing产生比较大的跳变,即Pre-CTS和Post-CTS的correlation问题。

要解决这个问题,需要工具能够在CTS之前就做出对于真实时钟树的预测,在Pre-CTS优化的时候就把时钟树这一重要因素考虑进去。这不仅仅可以帮助工具更早地看到时钟树buffer所占的空间,还可以更精准地对useful skew做出预判。

Clock Gating目前仍然是对于降低动态功耗最有效的方法之一。AI芯片自然也不会吝啬对于Clock Gating的使用。Clock Gating Cell(通常是Integrated Clock Gate,ICG)的enable path常常是时序优化的瓶颈。特别是高层ICG的时序,如果在Pre-CTS阶段不做一些额外处理的话,是难以修复的(图八)。这依然是要求工具能够提前对真实时钟树有一个预估,对useful skew的使用有所选择。

图八

2.AI芯片在功耗的表现上有几个特点:

1)动态功耗占据主导(图九)

当然,根据芯片设计、流片工艺和signoffcorner的不同,功耗也会有不同的变化。但是动态功耗相比于静态功耗,在AI芯片中的占比是要高得多的。比如,一个典型的比例是,动态功耗要占到总功耗的80%。这就意味着我们在实现的过程中,可以给与动态功耗以更高的优先级。

图九

还有一点值得注意的是,动态功耗由两部分组成:开关功耗(SwitchingPower)和内部功耗(InternalPower)。开关功耗指的是net上由于高低电平翻转,对负载电容充放电所带来的功耗。内部功耗则是standardcell内部翻转过程中产生的功耗,包括CMOS瞬时短路电流带来的功耗和cell内部的电容负载的功耗。AI芯片中的开关功耗和内部功耗更趋向于接近1:1的比例。也就意味着,除了通过对面积减少,降低transition来优化内部功耗之外,在开关功耗的优化上也有大量的工作可以做。比如,可以减少绕线的长度,可以restructure、pin swapping等逻辑优化。Innovus 18.1最新的版本有很多这些特殊处理的地方!

2)极不平衡的翻转率

关于功耗的另一个特点是net上的翻转率是极不平衡的。为了尽可能接近芯片真实的工作场景,翻转率的数值应该通过对网表的仿真,得到波形(VCD文件),然后折算出net的翻转率(TCF或者SAIF文件)。对于AI芯片来说,仿真应当运行真实场景中的深度学习算法。算法通常涉及到多个步骤(读写、卷积、池化……),则需要对各个步骤根据所运行时间的比例,求取加权平均后的求取加权平均后的翻转率。这样可以比较准确地反映出芯片工作时的平均动态功耗。

通过这种方法的到的翻转率,可以明显观察到,不同net直接的翻转率有着天壤之别(图十)。有一部分net翻转率非常高,几乎和时钟频率相近。他们几乎一直处于翻转的状态。而有一部分net的翻转率非常低,很久才翻转一次。甚至在典型的深度学习算法运行过程中,一次也没有翻转过,是一些非常安静的net。

图十

对于如此不同的net,我们在优化的时候自然不能一视同仁。一个很自然的想法就是,对于高翻转率的net,希望工具能尽可能减小它的线长,从而降低负载电容。这样它在不停地翻转时,开关功耗可以小一些。而对于非常安静的那些net,即使绕线长度长一些,只要并没有带来timing的问题,也是可以接受的。并不需要动用额外的资源去优化这些net。因为他们的翻转并不会花费多少功耗。

AI芯片的对于大吞吐量的追求使得它通常拥有流水线结构和并行的总线。如果可以充分利用这种结构也能够进一步优化动态功耗的表现。一个例子是,如果我们把版图上位置相近并且功能相同的寄存器替换为Multi-bit Flip Flop(图十一),动态功耗,特别是clock上的动态功耗是可以减少的。

图十一

之所以要求位置相近是因为不希望替换对timing带来影响。根据情况的不同,可以是2-bit、4-bit甚至8-bit的替换。这一点对于AI芯片并不难实现。因为总线上的寄存器在版图上的分布,由于前后连接关系的相似性常常会聚拢成堆,甚至多个寄存器在place之后自动就形成一个阵列。那很多MBFF的替换原地就可以进行,而对timing和routing不会带来什么影响。工具需要能够自动完成这一替换,并且在后续的时序优化中正确处理这些cell,在需要分拆的时候还原成单个寄存器。

3. AI芯片面积上的挑战表现在density和congestion上。

下图是几种类型芯片网表结构上的横向对比:

比如FlipFlop Ratio对比:

图十二

(欲知其他特性详情,请参加Cadence/ARM联合研讨会)。

AI芯片以上的特点,对工具应对high density、high congestion的能力提出了巨大的挑战。不仅要处理局部的routingcongestion,还需要面对全局的大面积拥塞。在确保routing没有问题的情况下,时序的功耗的目标仍然需要满足。

不同的Floorplan会对congestion以及timing的格局带来完全不同的变化。对极限指标的追求还需要从Floorplan上着手。需要工具提供更加自动、智能的方法,帮助Floorplan的优化,并且这种优化是需要全局考虑性能、功耗和面积的。

四、人工智能芯片实现的解决方案

针对前一节分析得出了AI芯片的特点,以及实现过程中的各种挑战,本节介绍了基于Cadence数字后端实现平台Innovus的优化解决方案,帮助芯片设计者更快地收敛到预期的性能、功耗和面积目标。

对于AI芯片开关功耗占比较多、翻转率差异较大的特点,基于真实仿真翻转率文件(Activity File)的动态功耗优化是非常重要的。在翻转率驱动的功耗优化方案上,最新的Innovus 18.1版本有着诸多的特性。比如:

·Power Optimization (activity-driven)

·Activity-Driven Placement

·Slack and Power-driven Placement

·Clock Power-Driven Placement

·High power effort CCopt

·Power-Driven Routing

·…

这里展示了在某款AI芯片核心模块上,逐步开启几种优化手段所得到的最终signoff功耗结果。

图十三

从结果可以看到,动态功耗得到了显著的降低。特别是SPP和CPD,充分利用了翻转率文件提供的信息,优先考虑高翻转率的Net,使其线长更短,降低功耗负载。而对于低翻转率的Net,允许放松线长的约束。

因此在没有影响timing的情况下,可以获得明显的开关功耗的优化。(更多的数据分析和细节展示,请参加Cadence和ARM的联合研讨会了解详情)

然后,让我们看看Innovus对于Congestion的解决方案。

正如前文的分析,AI芯片中大量的FlipFlop和多管脚单元,加上极致的面积目标,所以congestion往往变成了压死性能的最大的稻草。

图十四显示了版图的大部分区域都有非常严重的congestion问题。这种大范围的congestion是很难通过单纯的router的优化来解决的。更需要placer和router的相互配合,在flow的各个阶段通过对congestion的评估、把high congestion的区域cell density变得稀疏,同时保证timing得以满足。

图十四

从图十五可以看到,Innovus的High effort congestion repair非常好地给出了我们所期待的结果。中间congestion最严重的区域(红色的congestion marker),cell被尽量推开了,density降到很低(灰色部分)。推开的cell向四周挤进了congestion并不严重的区域。这些区域的density变得更高(黄色、绿色的部分),但是并没有关系,因为这些区域的绕线比较少,不会对congestion造成太大的问题。

图十五

但是图十五中在垂直方向的congestion依然过于严重了,虽然凭借Nanoroute的优化仍然可以全部绕通,但是不可避免会产生routing 的detour和timing的损失。

然,何以解忧?这里会用到Innovus的一个独门秘器,18.1亮点之一,行业唯一的解决方案。

效果如图十六,Timing、Density和DRC都得到了明显的提升。本来由于严重的congestion导致无法修复的大量Holdviolation也得以大幅改善。

·Performance:4%

·Wire Length :4.7%

·Area:0.3%

图十六

-

芯片

+关注

关注

446文章

47769浏览量

409067 -

人工智能

+关注

关注

1776文章

43824浏览量

230574

原文标题:研发分享:人工智能芯片的挑战与实现

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

分布式智慧终端:挑战与解决方案

联想集团举办芯片创新发展研讨会,论道研发存算“芯”挑战

AMD以技术赋能生成式AI算力解决方案

Art.Galaxy酷芯AI工具链解决方案

研华和Hailo联合推出可扩展、高能效边缘AI解决方案

AI智能呼叫中心

中国芯片消费量占全球50%,Synopsys.ai全栈式引领EDA+AI芯片设计,赋能汽车产业腾飞

浅析AI芯片的挑战与解决方案

浅析AI芯片的挑战与解决方案

评论