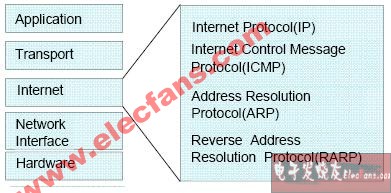

IP是英文Internet Protocol(网络之间互连的协议)的缩写,中文简称为“网协”,也就是为计算机网络相互连接进行通信而设计的协议。在因特网中,它是能使连接到网上的所有计算机网络实现相互通信的一套规则,规定了计算机在因特网上进行通信时应当遵守的规则。任何厂家生产的计算机系统,只要遵守 IP协议就可以与因特网互连互通。IP地址具有唯一性,根据用户性质的不同,可以分为5类。另外,IP还有进入防护,知识产权,指针寄存器等含义。

我们利用IP协议就可以使这些性能各异的网络在网络层上看起来好像是一个统一的网络。这种使用IP协议的虚拟互连网络简称为IP网。使用IP 网的好处是,当IP网上的各主机进行通信时,就好像在单个网络上通信一样,他们看不见互连的各网络的具体异构细节(如具体的编制方案,路由选择协议,等等)

IP网络的业务承载难题

在业务承载方面,虽然IP网络在QoS上有了很大的进步,但现有的IP网络大都只是在单个节点上提供相对优先权的处理。如果没有在全网层面上特别是在接入网中解决业务感知和接入允许控制,就不可能真正解决端到端的业务质量问题。此外现有IP网络在业务承载上的短板还体现在网络业务安全性和网络管理能力不足上。

IP是怎样实现网络互连的?各个厂家生产的网络系统和设备,如以太网、分组交换网等,它们相互之间不能互通,不能互通的主要原因是因为它们所传送数据的基本单元(技术上称之为“帧”)的格式不同。IP协议实际上是一套由软件程序组成的协议软件,它把各种不同“帧”统一转换成“IP数据包”格式,这种转换是因特网的一个最重要的特点,使所有各种计算机都能在因特网上实现互通,即具有“开放性”的特点。

数据包

在网络维护方面,自从IP技术进入到电信级商用领域,原有“尽力而为”传送的特性已不能满足电信级维护需求。IP网的非稳态故障出现几率远远高于交换、传输等其他电信网络,也会增加故障发现、分析和排除的时间和难度。

IP网维护的困境

虽然IP网维护存在很多问题,但IP网维护的困境主要由以下四个因素造成。

IP网网管能力偏弱

IP网的网管能力较交换、传输等专业偏弱,无论是早期的网元性能监控,还是现今常见的时延、丢包、抖动指标,都很难反映基于IP网的纷繁复杂的各类业务应用品质。

IP网业务支撑系统能力不足

IP网业务自动开通能力较弱,稍复杂的业务开通均需要手工配置。此外,维护人员水平的参差不齐造成对业务配置的理解和脚本实现都存在差异,从而增加维护成本和故障风险率。历史经验也告诉我们:70%的障碍都是人为造成的。

IP网设备故障率较高

IP网作为综合承载网,需要不断满足新的需求而部署新的功能,需要不断满足流量的增长而不断扩容,因此整个网络处于频繁的软、硬件升级过程中。其中,业务控制点作为IP网络结构中业务最复杂的网元,出现故障概率又远远高于其他网元,而恰恰在这个环节缺少有效的冗余安全保护。

4.IP协议开放性和统一的电信标准之间的矛盾

目前,IP协议标准的正式商用速度无法跟上越来越复杂的业务需求,IP协议内容也存在模糊地带,容易引起制造商理解不一致。这些因素都导致运营商对传统IP业务的管控能力较弱,缺少电信级维护手段。

如何运营好IP网络

从2001年南京城域网作为全国第一个宽带城域网开始运营以来,各个运营商都在思考如何将IP的低成本和电信级质量保障相互融合,我们认为可以从以下四个方面来进行。

运营商应更多的参与至整个IP产业链中

运营商应及早介入IP标准协议的制定,根据各类业务在实际运营中展现的特征,使IP网具备业务可控、可分析的电信网特性。

细分业务,IP网简单化

从应用层的优化降低对IP承载网的要求,尽量保持IP 网络的简单性。从技术上看,各类应用特性的不同需要IP网络不同的承载能力,可分为两大类业务:

“开放型“互联网业务主要为公众互联网访问业务,该类业务基本处于不可控制的“管道”状态,其流量呈现爆炸式增长趋势,业务模型特点为大带宽管道+“较差”的保障能力+智能的业务层终端设备,终端的智能化使得运营商的IP网迅速沦为管道;

“封闭型”自营性业务包括IPTV、语音业务等运营商自营业务及企业内部专线,此类业务的流量或内容完全可控,为运营商的关键盈利业务,业务模型特点为小带宽的电路+严格的保障能力+非智能的业务层终端设备,从终端、IP承载网、业务源均在运营商管控范围内,所以能提供全程QoS保障能力。

强化业务控制点功能

业务控制点加入DPI等功能,进一步加强业务流量管控和分析。同时提升业务控制点安全冗余能力,通过BAS热备和VRRP技术分别为公众客户和专线客户提供业务保护能力。

建立基于IP网的各类业务模型

通过对重点业务的体验监控,定期地收集网络性能和业务品质数据,通过分析数据,挖掘业务变化的趋势内容,基于时间等维度建立各类业务模型。既可以提升日常维护效率,又可以通过业务变化的趋势,为前端营销部门提供业务使用反馈和优化建议。

-

寄存器

+关注

关注

30文章

5020浏览量

117630 -

计算机

+关注

关注

19文章

6631浏览量

84375 -

IP

+关注

关注

5文章

1399浏览量

148262

发布评论请先 登录

相关推荐

IP网络维护的四大难题,如何运营好IP网络

IP网络维护的四大难题,如何运营好IP网络

评论