任意波形发生器( Arbit rary Waveform Generato r,AWG) 是一种多波型的信号发生器, 它不仅能产生正弦波、指数波等常规波形, 也可以表现出载波调制的多样化, 如: 产生调频、调幅、调相和脉冲调制等。更可以通过计算机软件实现波形的编辑, 从而生成用户所需要的各种任意波形。任意波形发生器的实现方案主要有程序控制输出、DMA 输出、可变时钟计数器寻址和直接数字频率合成( DDS) 等多种方式 。目前任意波形发生器的研制主要基于DDS 技术, 与传统的频率合成器相比, DDS 具有低成本、低功耗、高分辨率和快速转换时间等优点, 广泛使用在通信、测量与电子仪器领域, 是设备全数字化的一个关键技术。

1 任意波形发生器的理论分析

1. 1 DDS 技术简介

DDS( Direct Digital Sy nthesis) 的概念由美国学者J. T ier ncy、C. M. Rader 和B. Gold 在1971 年提出。该技术是从相位的概念进行频率合成, 主要优点是输出相位连续、相对带宽较大、频率分辨率很高、可编程、准确度和稳定度都比较高 。DDS 技术是利用查表法来产生波形, 而通过修改存储在ROM 里的数据, 就可以产生任意波形。

1. 2 DDS 基本结构

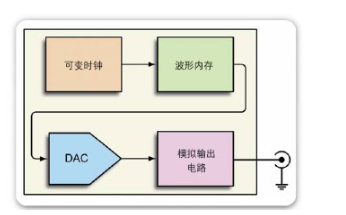

DDS 主要有相位累加器、ROM 波形查询表、数模转换器组成。其基本框图如图1 所示。

图1 DDS 结构框图

线性数字信号通过相位累加器逐级实现, 波形函数存储在ROM 中, 根据累加器输出的相位值作为地址,寻找存储在ROM 中的波形函数的幅度量化值, 完成相位到幅值的转换, 输出相对应的序列。

2. 1 设计方案

基于FPGA 实现DDS 功能, 通过单片机实现控制。此方案的核心在于FPGA 的设计实现逻辑功能,通过对存储器查表后输出信号, 由相连接的数模转换器转换为要求的波形。单片机作为控制器, 易于控制与调试。系统框图如图2 所示。

图2 系统框图

2. 2 D/ A 转换器的使用

本案采用德州仪器的TLC7528。它是双路、8 位D/ A 转换器, 本案设计为: A 路的数字量控制B 路的电压输出, B 路则控制输出的幅度。电路图可以显示,VA1( VOB1) 处输入的A( B) 路电压范围为- 5~ 0 V,VA2( VOB2) 处为A( B) 路的电压为- 5~ 5 V。DA 电路连接图如图3 所示。

图3 TLC7528 电路连接图

其中因为转换方法的问题, 产生的零点误差可以通过调整放大器的零点来校准; 而因为温度变化产生的温漂误差在技术上就比较难消除。关于单极性DAC 的增益误差可以通过调整放大器的闭环增益来消除。

2. 3 滤波器的设计

一般情况下, 椭圆滤波器的参数灵敏度最高, 在使用用相同阶数时, 椭圆滤波器能够得到最好的矩形系数, 7 阶椭圆滤波器在通带附近的频点可得到40 dB 的带外抑制, 很适合将杂散信号滤除。DDS 输出的另一类波形是频谱复杂的任意波形, 频率比较低, 频谱结构丰富, 具有较高的谐波分量, 选用等波纹误差线性相位滤波器来滤波, 它在很大范围内具有固定的延迟, 在远离截止频率处, 其幅度响应也比较好。

2. 4 单片机的设计

单片机采用传统8051 单片机, 晶振为12 MHz, 采用内部振荡方式; 复位输入引脚为高电平有效, 保持2 个机器周期以上的的高电平便可以实现对单片机的复位; 采用MAX232 芯片作为串口芯片, 单片机通过异步通信串行接口与其他计算机或者外围设备进行信息传递。

3 基于FPGA的DDS实现

FPGA 芯片采用ALT ERA 公司的CYCLON E 系列EP1C3T 144C8。设计采用Altera 公司的Quar tus , 使用AS 方式与JTAG 配置方式。

3. 1 固定波形输出

本案使用几个8 b 的ROM, 存储深度为1 024 点,用来存储正弦波等波形数据。每个波形数据存储在一个固定的ROM 里, 如图4Sine_ROM, Square _ROM等分别对应正弦、方波等存储模块。通过一个使能模块控制, 采取低电平有效的方式, 选择性读取任意模块的波形。输出波形时, 仅有单独一个ROM 工作, 其他模块为高电平, 保证输出所需固定波形。使能模块的输入端为行列式键盘, 设定为: 单键控制某一波形输出。

图4 波形ROM 与使能控制设计电路图

3. 2 任意波形输出

任意波形是由上位机下传的波形数据, 由单片机控制, 必须设计一个能随时接受数据更新的RAM。如图5所示。

图5 任意波形模块设计电路图

选用的D/ A 转换器为8 位, 所以RAM 的字长也为8 位, 因此波形RAM 的地址线的位数取10 位。为了实现任意波形数据的更新, 波形RAM 设计成为双口RAM。

4 性能与误差分析

4. 1 测试结果

输出波形如图6 所示。本系统测试所用到的仪器为:

示波器 T ekt ronix 公司 型号: T DS1012

计数器 创瑞科技有限公司 型号: SPF40

图6 输出波形图

4. 2 频率测量

通过设定预定值, 用计数器测量出实际值, 基于此数据计算出误差如下表( 只选取10 组数据) 。

由表1 可看出, 1 ~ 100 Hz 区间误差较为明显,1 kHz~ 1 MHz区间输出频率较为稳定( 该表为测试正弦波数据) 。

表1 频率数据表

4. 3 误差与杂散分析

除了工作环境与电源噪声等问题是影响到频谱纯净度的因素外, 还有以下主要原因:

( 1) 相位截断产生杂散信号。硬件上无法满足20 位的数据储存, 设计中均采用了高位截断的方法, 只取用累加器输出的高几位用于查表, 低位舍去。必然会造成误差从而影响最终的输出信号频谱。正弦信号上引入了余弦分量, 造成时域上的叠加, 必然表现为频域上的杂散。

( 2) D/ A 转换器非线性引起的杂散分量。理想DAC 对DDS 的影响只表现在对信号频谱的幅度和相位产生改变, 输出上体现出滚降特性, 并不引入其它的频率成分, 而非理想的DAC 的非线性、瞬间毛刺等非理想的转换特性在输出频谱中产生了杂散。

( 3) 幅度量化产生的杂散。正弦查表内存储的波形码事一个模拟信号被均匀量化后的值。存储器的容量有限, 不可能以无限二进制数来记录正弦值, 因此出现幅度量化误差。

减小DDS 输出电压中的杂散及噪声的方法, 除了选用性能优良、工艺精湛的D/ A 转换器, 提高位数与幅度量化字长外, 还可以通过设计良好的低通滤波器, 以滤除各种杂散及带外噪声, 也可选用DDS+ PLL 频率合成技术, 以及数据压缩法, 最高压缩比可达128 1。另外可以在产生的相位字序列上加入高频抖动( Dither) , 因为相位截位误差成周期分布, 这将导致在某些频率处产生较大的毛刺, 使DDS 产生的频谱无杂波动态范围减小。通过在相位上加入抖动, 能够破坏相位误差中较明显的周期性分布, 从而使得毛刺的幅值得到减小, 增大了输出正余弦波的无杂波动态范围 。

还可以采用相位误差反馈结构, 在SCMF( 相位累加器和正余弦函数生成器) 前加入一个二阶FIR 滤波器( Finite Impulse Response, 有限冲击响应) 来滤除输出频率附近的相位误差。

5 结 语

任意波形发生器的设计是全国电子设计大赛中经典的选题之一, 任意波形发生器的设计不仅有广泛的实践应用空间, 并且对于电子科的学生动手能力的提高及学科知识的融会贯通同样具有极大的指导价值。本文寻求功能强大、操作便捷、输出参数稳定的设计效果, 并主要偏重基础, 使之更符合教科书的典型教学条件, 并对相关参数进行测量, 分析原因。关于波形发生器的设计, 仍有许多可以设计扩展的功能, 杂散的削弱仍有较多的方法值得探究。

-

FPGA

+关注

关注

1602文章

21309浏览量

593127 -

DDS

+关注

关注

21文章

614浏览量

151729 -

波形发生器

+关注

关注

3文章

284浏览量

31186

发布评论请先 登录

相关推荐

【Z-turn Board试用体验】+基于FPGA和DDS技术的三相正弦波的发生器设计

函数信号发生器是否与任意波形信号发生器相同

任意波形发生器_DDS任意波形发生器的设计

基于Verilog实现的DDS任意波形发生器

利用FPGA实现DDS技术实际任意波形发生器

利用FPGA实现DDS技术实际任意波形发生器

评论