1、引言

嵌入式系统在日常生活中的大量使用,人们也对其性能和速度提出了更高的要求。微控制器和可编程逻辑器件的结合,更能充分发挥嵌入式系统的优势。本文设计和实现的微控制器与可编程逻辑器件之间总线读写方式通信比传统的串行通信更可靠、速度更快。下面是一些相关术语的说明。

总线:任何一个微处理器都要与一定数量的部件和外围设备连接,但如果将各部件和每一种外围设备都分别用一组线路与CPU直接连接,那么连线将会错综复杂,甚至难以实现。为了简化硬件电路设计、简化系统结构,常用一组线路,配置以适当的接口电路,与各部件和外围设备连接,这组共用的连接线路被称为总线[2]。采用总线结构便于部件和设备的扩充,尤其制定了统一的总线标准则容易使不同设备间实现互连。

AVR:ATMEL公司的AVR单片机,是增强型RISC内载Flash的单片机,芯片上的Flash存储器附在用户的产品中,可随时编程,再编程,使用户的产品设计容易,更新换代方便。AVR单片机采用增强的RISC结构 ,使其具有高速处理能力,在一个时钟周期内可执行复杂的指令。本系统采用的AVR Mega64L还具有:用32个通用工作寄存器代替累加器,从而可以避免传统的累加器和存储器之间的数据传送造成的瓶颈现象;一个时钟周期执行一条指令;可直接访问8M字节程序存储器和8M字节数据存储器寄存器等特点[3]。

PLD(Programmable Logic Device):PLD分为CPLD(Complex Programmable Logic Device)复杂的可编程逻辑器件和FPGA(Field Programmable Gate Array)现场可编程门阵列两大类[2、3]。

两者的功能基本相同,只是实现原理略有不同,所以我们有时可以忽略这两者的区别,统称为可编程逻辑器件或CPLD/FPGA。PLD是一种具有丰富的可编程I/O引脚的可编程逻辑器件,具有在系统可编程、使用方便灵活的特点;不但可实现常规的逻辑器件功能,还可实现复杂的时序逻辑功能。把PLD应用于嵌入式应用系统,同单片机结合起来更能体现其在系统可编程、使用方便灵活的特点。PLD同单片机接口,可以作为单片机的一个外设,实现单片机所要求的功能。实现了嵌入式应用系统的灵活性,可以大大缩短设计时间,减少PCB面积,也提高了嵌入式应用系统的性能。

VHLD:VHDL的英文全名是Very-High-Speed Integrated Circuit Hardware Description Language,一种被IEEE和美国国防部确认为标准硬件描述语言。VHDL主要用于描述数字系统的结构、行为、功能和接口。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分)和内部(或称不可视部分),涉及实体的内部功能和算法完成部分[4,5]。在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

2、PLD同单片机接口设计

系统中采用的MAX II EPM570 芯片有逻辑单元数(LE)570个,等效典型宏单元数440个,最大用户I/O管脚数160个,用户Flash存储器比特数8192,tPD1 角对角性能5.5 ns,tPD2最快性能3.7 ns。采用100-pin TQFP封装。

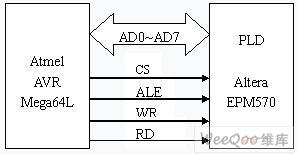

EPM570同单片机接口原理如图1所示。

图1 ATmega64L与EPM570接口示意图

EPM570同单片机接口设计中,单片机采用Atmel公司的AVR系列的ATmega64L。ATmega64L通过ALE、CS、RD、WE、P0口(数据地址复用)同EPM570芯片相连接。ALE:地址锁存信号;CS:片选信号;RD:读信号;WR:写信号;AD0~AD7:数据地址信号复用数据线。

本系统的设计思想是:在EPM570设置两个内部控制寄存器,通过单片机对两个控制寄存器的读写来完成对其它通信过程的控制。EPM570设置的两个控制寄存器,可以作内部寄存器,也可以直接映射为I/O口,根据实际需要而进行设置。

本系统设计的关键是:在EMP570 上实现的存储器的读写时序要满足ATmega64L对外部读写时序的需要,有关ATmega64L对外部读写时序请参考相关资料和ATmega64L的数据手册。

3、PLD同单片机AVR读写接口VHDL实现

PLD的设计流程[6,7]一般应包括以下几部分:

① 设计输入。可以采用原理图输入、DHL语言描述、EDIF网表读入或波形输入等方式。

② 功能仿真。此时为零延时模式,主要检验输入是否有误。

③ 编译。主要完成器件的选取及适配,逻辑的综合及器件的装入,延时信息的提取。

④ 后仿真。将编译产生的延时信息加入到设计中,进行布局布线后的仿真,是与实际器件工作时的情况基本相同的仿真。

⑤ 编程验证。有后仿真确认的配置文件下载到PLD相关配置器件中,加入实际激励,进行测试,以检查是否完成预定功能。

以上各步骤若出现错误现象,则需要重新回到设计阶段,修正错误输入或调整电路,在重复上述过程直到其完全满足电子系统需要。

本系统中,使用Altera公司提供的集成开发软件Quartus II 6.0 进行设计,在进行模块实现时请参考ATmega64L的数据手册中关于ATmega64L对外部存储器的读写时序。

本设计实现 的VHDL部分源码如下:

地址锁存:

写数据进程:

读数据进程:

4、仿真验证结果

使用Quartus II 6.0 自带的仿真软件仿真结果如图2和图3所示。图中ale、cs、rd、we、mcu_data 是激励信号,表示ATmega64L 相应接口信号,conreg1和 conreg2 为EPM570 输出信号,其目的是为了观察仿真结果是否正确,而实际应用中应根据项目需求而进行添加或是减少相应的I/O口。

图2是ATmega64L向 EPM570 写数据过程。首先,在片选信号cs为低期间,在ale信号的下降沿,锁存mcu_data上的数据到add内部地址锁存寄存器。然后,在we信号低电平时,把mcu_data (0XAA)的数据直接写到conreg1(B10101010),通过外接指示灯可以直接观察结果是否正确,当然,在实际应用中可以把数据锁存到内部寄存器中。

图2写数据0X“AA”到0地址处

图3是读数据过程。在片选信号为低期间,首先,在ale信号的下降沿,锁存mcu_data(0X01)数据到add内部地址锁存寄存器。然后,在rd信号的低电平期间,把内部寄存器地址为0X01的数据reg02(0xAA)读到mcu_data数据线上传回单片机ATmega64L。

图3 读地址为0X“01”上的数据0x“AA”并传回数据总线

从读写数据图中可以看出,ATmega64L对EPM570内部数据读写过程完全满足ATmega64L数据手册上的时序需要。关于ATmega64L的读写时序可以参考ATmega64L数据手册。

5、结语

本文实现PLD与AVR ATmega64L通信接口设计是笔者设计的一种纺织机械控制设备的一部分,经实际验证完全正确,并已投入生产。简单地修改该读写通信模块,可应用于多个CPLD或FPGA与单片机通信接口的项目中,本模块还可以根据需要扩展为16位、32位地址线的读写接口。

本文创新点:充分利用可编程逻辑器件丰富的I/O口和内部可编程逻辑资源,通过总线读写的方式通讯,使PLD和MCU的通信速度大大提高,同时也提高了嵌入式系统或是工业控制中的其他相关性能,极大提高产品的竞争力。

-

微控制器

+关注

关注

48文章

6806浏览量

147600 -

嵌入式

+关注

关注

4981文章

18271浏览量

288289 -

可编程逻辑

+关注

关注

7文章

511浏览量

43903

发布评论请先 登录

相关推荐

基于AVR单片机和PDIUSBD12的USB接口设计

基于AVR单片机和PDIUSBD12的USB接口设计

基于AVR单片机和PDIUSBD12的USB接口设计

求助求助 关于AVR SPI接口通信

AVR与FPGA通过SPI接口通信

基于PLD的视频接口

采用PLD实现视频接口设计

应用PLD实现初始化过程和所有数据传输

基于AVR的网络用具接口的设计与实现

利用PSD834F2中的PLD实现串行通信扩展的设计

如何实现PLD与AVR通信接口设计

如何实现PLD与AVR通信接口设计

评论